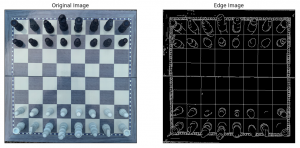

For the previous two weeks, I have been working on board-detection to accurately detect every corner of the board. Last week, I tried to use edge detection to retrieve all the edges from the board and then find the rectangular shape of the tiles. Below are the images of my approach for board-detection using edge detection.

As you can see from the image, it looks like it cannot find the squares (tiles) of the board but detect other parts of the board which are irrelevant to board-detection. So, as we decided that we would first detect the corners of the board before the pieces are places, I had to put this approach aside and try with a different approach.

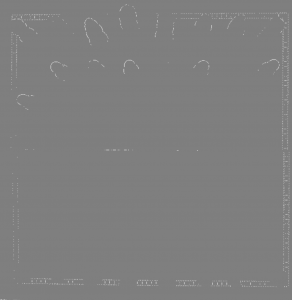

Previously, 49 (7×7) corners could be detected from the function that OpenCV provides. However, I couldn’t detect the entire 81(9×9) corners since the function that OpenCV provides wasn’t able to detect all corners. Since we know that square tiles are separated equally from each square, I calculated the average distance between each of the corners and used the calculated value to predict the rest of the corners. The image below shows the result of the 9×9 corner detections.

(We are using HSV space, but the circles in green will not show clearly on HSV space, so for this report, I converted back to RGB space so that the corners detected are easy to see.)

In addition, I implemented a function that could find the position on the board given an x and y coordinate so that Joseph can use this function in the future to find out which piece has moved and where the piece has moved. So, I believe I have finished the board detection part, although there might be some improvements in the future.

Next week, I will start working on the User Interface part of our project so that once Joseph finishes his computer vision part, we can integrate the User Interface and Computer Vision to test whether they are working correctly.