This week we worked on finalizing our design and made several changes based on TA/Instructor feedback. As such we will be using hard processor system (HPS) on the FPGA chip as well as an RPi to interface with the HPS. We decided on this because it would ease the integration steps as I will be the only member with access to the FPGA.

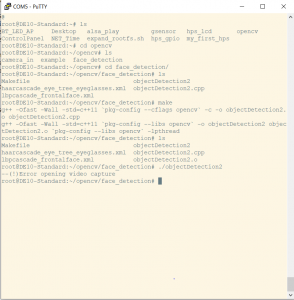

As for scheduled tasks, I have set up the Intel default linux distribution onto the FPGA’s HPS and also set up serial communication between the HPS and my computer. This process will be similar to what we imagine our final integration will look like with two programs interfacing with one another via the UART system. Rather than streaming the entire Linux OS output via UART. Basic UART communication between my computer and the FPGA is pictured below.

I have also begun sketching out some of the basic rules and board representations which I will need to consider when generation legal moves via FPGA custom hardware.

https://www.chessprogramming.org/Board_Representation

https://www.chessprogramming.org/Move_Generation

These two link describe the basics which my system verilog implementation must consider. I have also looked over the stockfish open source code to see what slight modifications I will need to make to it to make use of the additions I am planning. Specifically, I should be looking at modifying move generation.

That’s all for this week, next week I will make more progress into working with the HPS and also continue with my system verilog implementation.