This week we finished the final presentation and presented. We also finished integration and all components seem to work together correctly. In the next 2 days we will finish getting all the video clips for the final demo video and also set up the poster. We seem to be on schedule to finish within the Monday deadline.

Michael’s Status Report for 5/8/2021

This week we finished our presentation and also finished integration after that. I fixed the UART bug that was discussed in the presentation and have also gotten the metrics missing because of the bug. Lastly we will get clips for the video and edit the video in the following days.

Team status report 5/1/2021

This week we spent a few days to integrate all the systems together. As we discussed with our TA and Prof, we swapped out the RPi due to the UI running very slowly on it. We have also completed some benchmarking of the correctness of the system as will be required to present this coming week. Some speed testing of the UART communication was also completed as well as the correctness of the FPGA module.

Overall, we need to still fix the UART communication as although some messages work, the entire system does not yet work. This is the main goal for the next week once we have presented.

Michaels Status Report for 5/1/2021

This week we all worked together to bring the entire project together. As the others have stated, we are a little behind on the FPGA integration as communication between the FPGA and PC is a little off due to the both platforms needing to read and write. I am currently debugging the pyserial modules which both the FPGA and Game UI utilize to communicate with one another.

Michaels Status Report for 4/24/2021

This week we worked together to integrate all of our components together. For me, we have integrated the FPGA together with the UI such that the UI is able to send moves over the UART communication channel and the FPGA HPS is able to process the input in the correct way.

A blockade that we had to overcome was an outdated version of python which the FPGA HPS came with so I had to reinstall python3.7 by compilation. I had a few other compilation issues having to do with armv7 with stockfish and other programs that needed to run on the FPGA HPS but I have solved those now.

We are mostly done with our integration and mostly now just focus on some of the features which we would like to implement such as the suggestion of multiple moves by stockfish. I am on schedule with my part of the integration and it seems everyone is doing well as well.

Michael’s Status Report 4/10/2021

This week I continued to work on the edge cases for legal move generation. Specifically the cases for en passant is tricky because it requires knowledge of the exact previous move and the move is a capture which does not capture on the square which the capturing piece moves to. Hence, there a quite a few extra components to that logic than originally anticipated.

Otherwise, progress on SV and FPGA seems to be going well. I will demo a quick testbenches of a few board states on Monday using the waveform viewer. After that the plan for this week is to finish the legal move generation including edge cases and begin integration with the FPGA and HPS.

Michael’s Status Report 4/3/2021

This week I worked exclusively on system Verilog coding. I have completed all of the logic needed for basic moves such as bishop, rook, pawn, queen and knight movement.

I still need to verify the valid move generation works as intended, expect this to be completed towards the beginning of the next week. I will simply feed in a series of board states to the module and verify by hand on a waveform simulation.

There are a lot of other more subtle moves which I need to complete next week, including castling, castling through check, en passant, etc.

Looking at the schedule, it seems that the original time allocated to pipelining is being eaten into, but I am pipelining as I go through each different type of move. The hope is that everything is completed at the originally intended time, and I am confident in that happening.

Michael’s weekly status report

This week, I worked on synthesizing my custom logic onto FPGA. I had a driver issue that took a while to fix as Intel’s documentation is not the greatest, but everything should run smoothly from now on. I am also continuing to write more verilog code and am getting close to a point at which I can write a simulation testbench and also test on FPGA with its buttons as inputs, or possibly setting a memory mapped register with testbench values. Expect more progress in this direction for next week, and a fully working Game State Logic/Valid moves for 1 Square next week.

I also received a VGA cable from Quinn to help debug anything on the FPGA’s HPS and a quick task I can try next week is to run an unmodified stockfish program on the HPS to verify there will be little problems in its integration. I am still on track to complete Game State Logic/Valid moves for 1 Square as specified in the Gantt chart by next week, which is again 1 week behind our original schedule but I took an extra week to work on HPS/FPGA integration as our original plan had changed. Hopefully that work into integration will save us time when doing a full integration, and hence, I am hopefully still on track.

Michael’s Status Report for 03/13/2021

This week I worked on continuing HPS (arm core), FPGA integration. I want to fully understand the options for HPS and FPGA before continuing my Verilog implementation so that I know all my options for the full integration. This was a new objective I needed to add for this week so I am slightly behind the schedule now but I am hopeful that I have allotted more than enough time for the Verilog portion of the project.

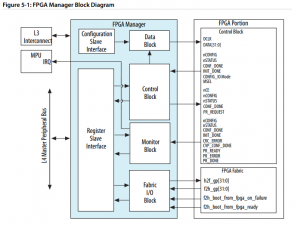

Specifically this week I have worked through examples from the DE10-standard manual:

https://www.intel.com/content/dam/altera-www/global/en_US/portal/dsn/42/doc-us-dsnbk-42-5505271707235-de10-standard-user-manual-sm.pdf

I worked through some of the examples in chapter 5, 6, 7 and 9, while also reading through a more thorough description of the HPS in another manual:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv_54028.pdf

Specifically, I have looked into beginning to understand the integration component of the HPS and FPGA and ensuring now that I have a plan for integration later so that when coding Verilog, I can ensure that the correct registers are loaded with data needed to feed into stockfish.

Although it may seem I am behind on game state logic, I have spent this week preparing part of the integration between stockfish and my custom logic. Ultimately, both will be needed in a complete project and this additional task came up because of a system design change we made after feedback. Hence, my schedule looks ok.

Michael’s Status Report for 3/6/2021

This week we worked on finalizing our design and made several changes based on TA/Instructor feedback. As such we will be using hard processor system (HPS) on the FPGA chip as well as an RPi to interface with the HPS. We decided on this because it would ease the integration steps as I will be the only member with access to the FPGA.

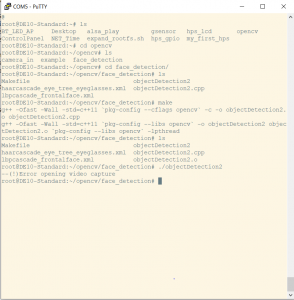

As for scheduled tasks, I have set up the Intel default linux distribution onto the FPGA’s HPS and also set up serial communication between the HPS and my computer. This process will be similar to what we imagine our final integration will look like with two programs interfacing with one another via the UART system. Rather than streaming the entire Linux OS output via UART. Basic UART communication between my computer and the FPGA is pictured below.

I have also begun sketching out some of the basic rules and board representations which I will need to consider when generation legal moves via FPGA custom hardware.

https://www.chessprogramming.org/Board_Representation

https://www.chessprogramming.org/Move_Generation

These two link describe the basics which my system verilog implementation must consider. I have also looked over the stockfish open source code to see what slight modifications I will need to make to it to make use of the additions I am planning. Specifically, I should be looking at modifying move generation.

That’s all for this week, next week I will make more progress into working with the HPS and also continue with my system verilog implementation.