This week I worked on continuing HPS (arm core), FPGA integration. I want to fully understand the options for HPS and FPGA before continuing my Verilog implementation so that I know all my options for the full integration. This was a new objective I needed to add for this week so I am slightly behind the schedule now but I am hopeful that I have allotted more than enough time for the Verilog portion of the project.

Specifically this week I have worked through examples from the DE10-standard manual:

https://www.intel.com/content/dam/altera-www/global/en_US/portal/dsn/42/doc-us-dsnbk-42-5505271707235-de10-standard-user-manual-sm.pdf

I worked through some of the examples in chapter 5, 6, 7 and 9, while also reading through a more thorough description of the HPS in another manual:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv_54028.pdf

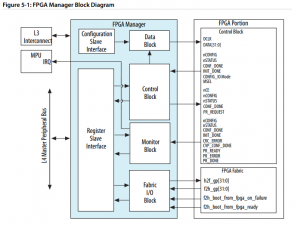

Specifically, I have looked into beginning to understand the integration component of the HPS and FPGA and ensuring now that I have a plan for integration later so that when coding Verilog, I can ensure that the correct registers are loaded with data needed to feed into stockfish.

Although it may seem I am behind on game state logic, I have spent this week preparing part of the integration between stockfish and my custom logic. Ultimately, both will be needed in a complete project and this additional task came up because of a system design change we made after feedback. Hence, my schedule looks ok.