Manav’s Status Update for 11/21

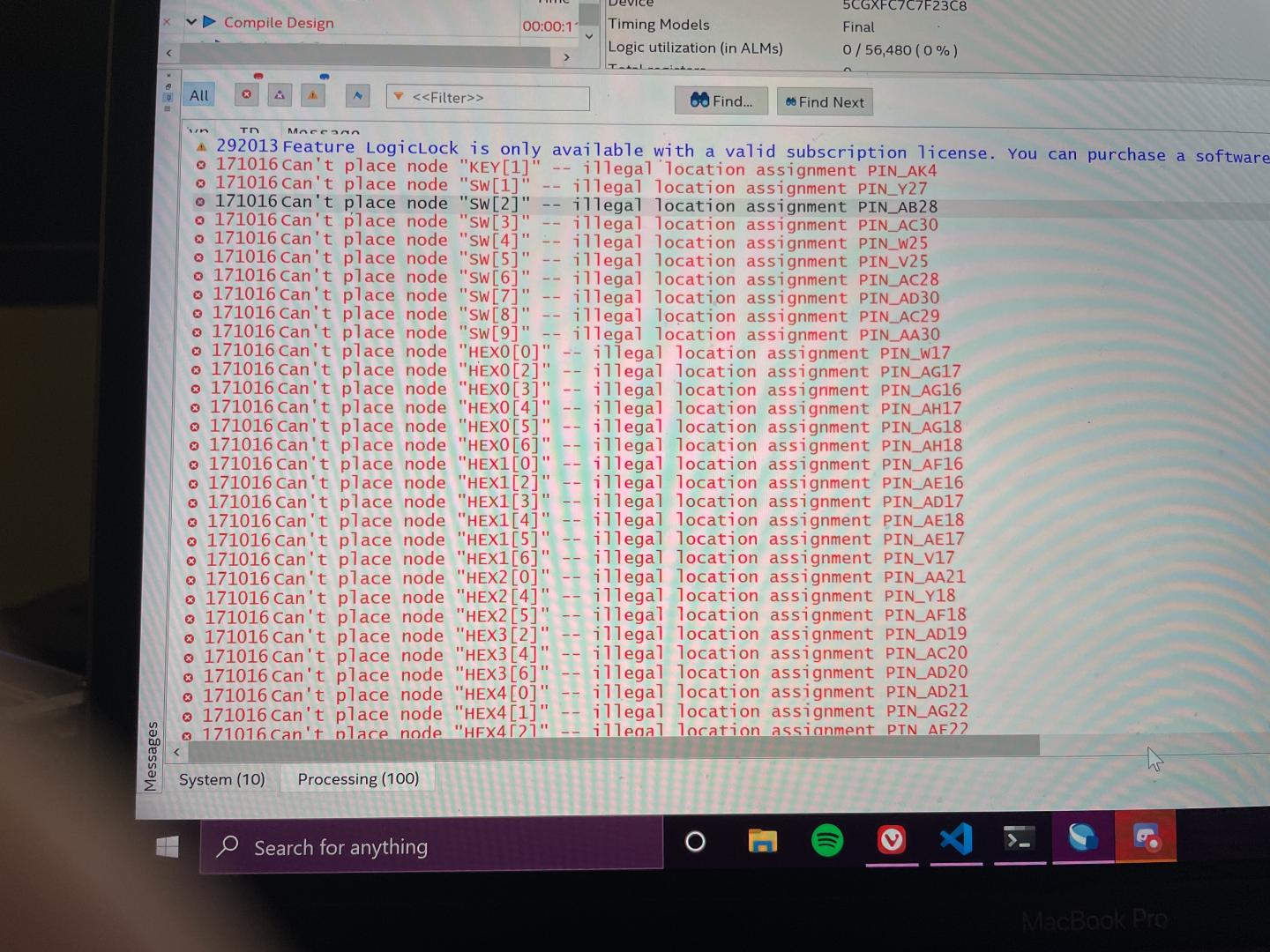

This week, I spent a lot of time trying to make sure that I could get the hardware working and get my parts of the product properly synthesized. In terms of going from MIDI keyboard press to usable data packets for the audio processing units, I have almost everything in place. I also ended up writing up the top-level module for our project to connect all the pieces we currently have together. This module currently integrated all the code that I have written for the audio layer up until now. I also created the circuits for the DAC, MIDI keyboard, and connected everything up to the FPGA. One issue that cropped up was that we realized that MIDI keyboard outputs an integer for the pitch of the sound that had been played when we need the fixed point decimal equivalent of that for the wavetable oscillator. In order to resolve this, we needed a way to convert an integer to a fixed point, without incurring too much of a cycle deficit. The threshold we had for cycles was a bit abstract since we don’t know how many cycles of latency we will incur for the actual audio processing, along with the fact that we don’t know how tight the multiplier count will be, so after consulting with my team, we ultimately decided a combinational lookup table would likely be the best option of this issue. So I ended up creating a python file that generates a SystemVerilog code that I can input into my module to take in the midi pitch and output it as a frequency pitch. So now I know that the pitch and velocity that is passed to the audio processing unit is in the expected form. In addition to this, the output produced by the audio processing unit was a 32-bit packet, so I created another module to turn into a serial output that could be interpreted and used by the hardware. In addition to this, in order to correctly observe whether or not the MIDI was being decoded properly, I created an interface with the on-hardware seven segment displays to present the decoded note_on, note_off, pitch, and velocity messages that it decoded. The issue we are currently plagued with is that the pinout that we are using for the FPGA we are using doesn’t seem to work as expected and has incorrect mappings for a lot of pins, which has resulted in us being unable to test in synthesis. Due to the school’s policy on coronavirus, my groupmate and I are all parting ways when we go home, so I handed off all of my completed circuits and hardware elements to Eric so we can run things once he gets to testing his part in synthesis as well. I plan on working on the event dispatcher and mixer now and try to integrate it with the remainder of our project since it seems like the current parts work in simulation.