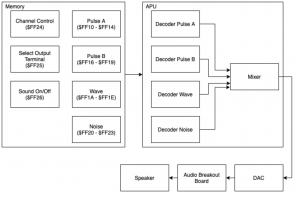

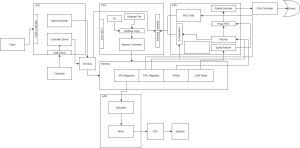

This week we focused on getting the CPU running and booting the board and transferring files to the SoC. Tess and Adolfo focused on getting the CPU running. They started by finishing the code. A majority of the code was complete but they had to polish the connections between the different components and cleaning the ISA and signals file. Once this was done, they compiled each file individually. Once they could compile each file individually, they compiled the datapath to the magic memory they created based on the 18341 P6. Currently, they are working on debugging it with unit tests they created and they hope to have it debugged by the end of the week so they can incorporate interrupts and the PPU.

Additionally, Tess and Adolfo will need to work on learning how to handle interrupts in the multi-cycle instructions in order to stay cycle-accurate.

Pratyusha focused on getting the board booted up. She established serial connection with the VM and the board. She was able to boot the board with the console version of linux. Additionally , she managed to run a hello world program, configured fpga trough soc and turn on leds. Her next goal is to transfer files to the SoC, look into Memory mapped RAM and controller driver.

Tess updated the risk management plan. The team worked on Gantt chart to include the new risk and mitigation plan created by the remote access situation: