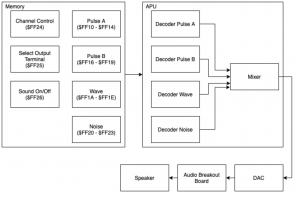

This week we focused on getting ROM0 games to run on the FPGA. This required finding all the small timing and memory bugs that were created by having the memory accesses at a different clock speed. To resolve this, we made our simulation model mimic our hardware model. Additionally, we made as much memory combinational read, meaning an array, to make the transfer easier. Once we were able to get all the synthesis issues and base logic worked out, we got Tetris and Dr. Mario running on hardware!

I spent a majority of the week working on the MBC. I implemented MBC1, MBC3, and MBC5 based on the different documents and reports that people in the community. I worked on debugging through the tests, but towards the end of the week I passed it to Adolfo and started working on the final report and presentation. Due to the refocus, we wanted to make sure we had enough time to implement all the changes. Therefore, I started and lead updating and creating our final report and presentation. Once the presentation is done, I will work with Adolfo to finish getting MBC working on the FPGA.

Goals for next week:

- Get MBC1, MBC3, and MBC5 working on the FPGA to run more complex games

- Polish code to match coding standard

- Finish report