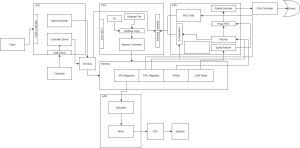

This week Adolfo and Tess focused on getting ROM0 games running on the FPGA. Together the worked on smoothing out the final timing and memory bugs that came up when implementing the work around for combinational read on the FPGA. Once Tetris start running, Tess focused on debugging MBC1 and MBC3. Adolfo worked on fixing the small PPU bug that became apparent when running Dr. Mario.

Once Dr. Mario was running, Adolfo took over debugging the MBCs and Tess start updating and creating the final report and final presentation. Adolfo debugged the MBC by creating a small FSM to support the boot rom process, and allowing memory to dynamically adjust the different cartridge and ROM size. He was able to get it working in simulation, but there is still an issue with MBC on the board. Adolfo and Tess will investigate this once the presentation is over.

Additionally, while Adolfo was working on getting larger games onto the board, our on chip memory isn’t big enough to run games larger than 512 kB. To work around this, Professor Nace has given a new board so once we figure out the MBC bug we will move to the new board to try larger games.

Pratyusha and Adolfo setup the SoC on Adolfo’s board, and we were able to transfer and run the controller binary on Adolfo’s board, with controller unit tests passing. They ran into unforseen problem where they couldn’t flash the FPGA without stopping the program on SoC , and couldn’t have the program on FPGA keep running while executing the SoC program. We expected the HPS program and the FPGA program to both proceed simultaneously and talk to fpga peripherals.

To fix this, we first tried to get qsys, a system design integration tool, running on Adolfo’s laptop, but due to a bug with Windows/Qsys we couldn’t run Qsys on his laptop. For this temporary hitch, Adolfo used an RPI to processor controller inputs while Pratyusha worked on Qsys. Now, she can run a program on SoC while flashing FPGA with a different program.

As a team, we will work on finishing the presentation this weekend and preparing for the presentation on Monday. Once the presentation is over, we will focus on finishing the report. Adolfo and Tess will also focus on determining the MBC bug, and then polishing the code and repo.