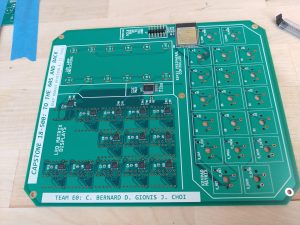

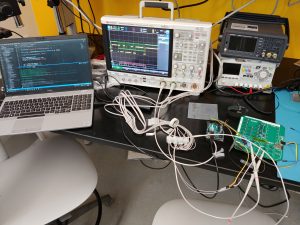

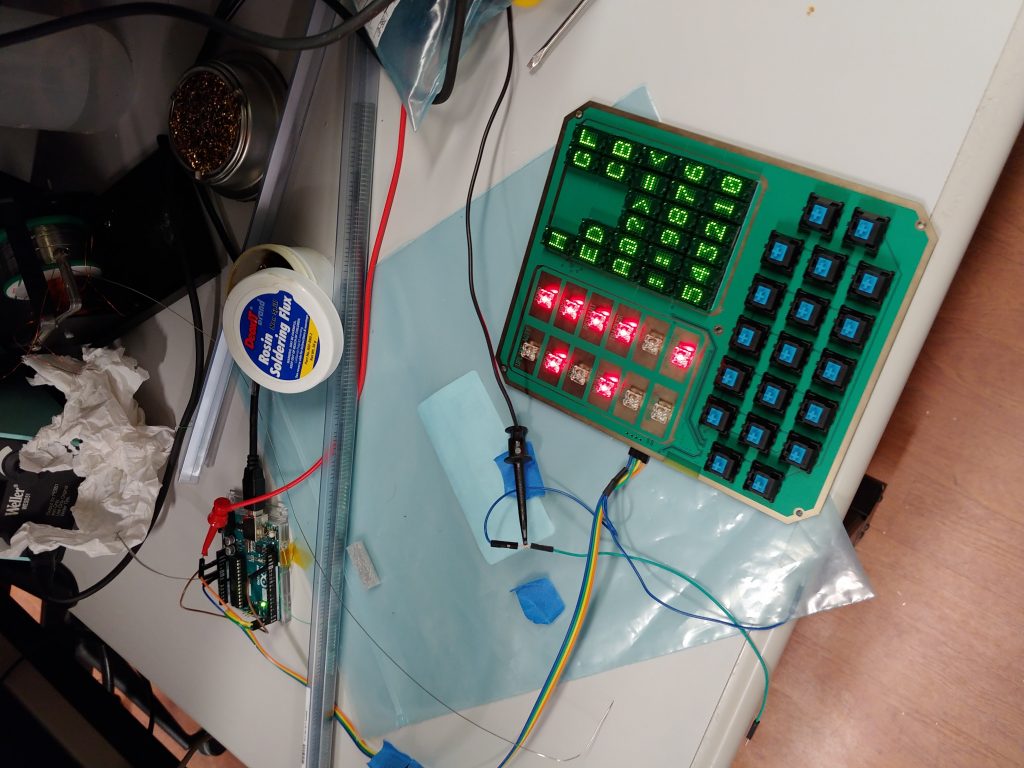

This week I was responsible for working with Don to make sure the microcontroller on the DSKY and the I/O driver that Don was building spoke with common protocol. Since we were using UART, we decided to go for a plaintext communication such that we can easily debug using a serial terminal window. We gained insight into how to send display data packets to the DSKY and how the DSKY was going to send NOUN/VERB numbers to the AGC core.

I was also responsible for bringing up and verifying that the math functions (SIN, COS, SQRT) were operational and accurate. These functions were from the original Apollo missions so therefore they were well implemented, We are now ready to start writing code for the demo and test on the architecture once it is up and running.