This week I worked on finishing the FSMs to manage the CPU when there are multi-cycle instructions. Last week, Adolfo and I determined that we would need either one big FSM with multiple branches or multiple smaller ones. We decided to make the smaller ones. I worked on the FSM for the 8-bit ALU operations, 16-bit add operations, pop/push, inc/dec, and CB instructions. Adolfo and Pratyusha are finishing the final 2 FSMs. During this process, I realized there were a lot of flaws in our original CPU datapath so I was updating it with needed connections.

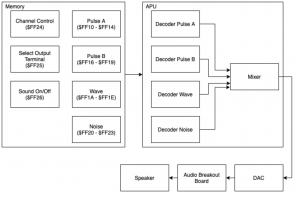

Afterwards, I did more research into how the Game Boy audio works. To save space, the Game Boy had a real time synthesizer because holding an entire audio file in the cartridge took up too much space. There are 4 voices with 5 registers each. Two of the voices are pulse waves that produce the tone. One voice defines the wave shape and the other is used to output white noise. The bits in the register define the voice so each wave needs its own decoder because the bits are in different locations and mean different things depending on which wave you’re looking at. From there, the voices are mixed together and controlled by 3 sound controlling registers. With this information, I was able to design a preliminary datapath for the APU:

With knowing more about the audio, I was able to select and order at DAC. I selected the Monolithic 16-bit AD669 DAC. It is 16-bit with parallel transfer and has a sampling frequency that will be more than suffice for our sound quality. Additionally, it is a through-hole chip, so we need to wire the GPIO pins of the development board to a breadboard. To get the audio into a speaker, we also had to purchase an audio jack breakout board.

Action items for next report:

- Design how the mixer will work

- Read through DAC manual to know what circuit requirements are needed

- Implement FSMs for CPU