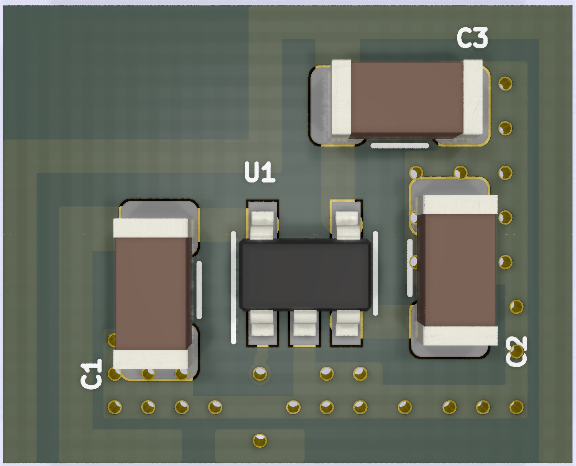

This week, I worked on generating a preliminary layout for the motor controller board in KiCad. To accomplish this, I finished specifying and laying out an 8V LDO-based supply for the motor controller ICs:

It’s laid out in standard-cell format so that it can be easily dropped into the final motor controller board. We came up with an initial BOM for this supply for the design report, but I ended up revising it to better reflect the requirements stated in the voltage regulator’s datasheet: https://www.digikey.com/short/z8pr24. The revised BOM simply includes two large I/O capacitors, so there isn’t much of a change to the budget. The specific IC is the LK112M80TR (rated for 150 mA of output current). Fortunately, the low quiescent current draw of the motor driver ICs (22.8 mA in total for each controller board) means that we don’t need to include thermal considerations during layout design. It takes a 23.5 C temperature rise to produce a 1dB degradation of supply voltage rejection for this particular regulator (the key spec for a LDO), and it’s incredibly difficult to produce that with only 91 mW of quiescent power consumption.

I’ve also produced a PDF of the tentative full schematic for the motor controller: KiCad Schematic

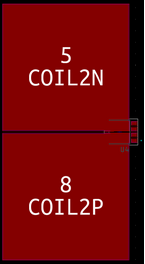

At the moment, the layout of the motor controller board is being held up by the unwieldy footprints of the MOSFETs. Each MOSFET drain requires a 28 mm by 28 mm copper square to keep their temperatures below ~35 C during operation, resulting in this horrid thing:

It doesn’t help that the MOSFET drains are on one side of the package while the sources and gates are on the other, since drains and sources need to be connected in a H-bridge. I’ve gotten around this thus far by using one MOSFET in each IC (the ICs have 2 MOSFETs each) for individual half-bridges, but it requires excessive distance between the MOSFET gates and gate drivers (terrible for minimizing H-bridge ringing).

Luckily, there haven’t been any issues with copy-pasting the standard cells for the power supplies into the full motor controller KiCad project. I was initially worried when I figured out that it’s not possible to directly copy-paste between KiCad instances, but it turns out that EESchema allows users to append schematics, while the standalone version of PCBnew allows for appending layouts.

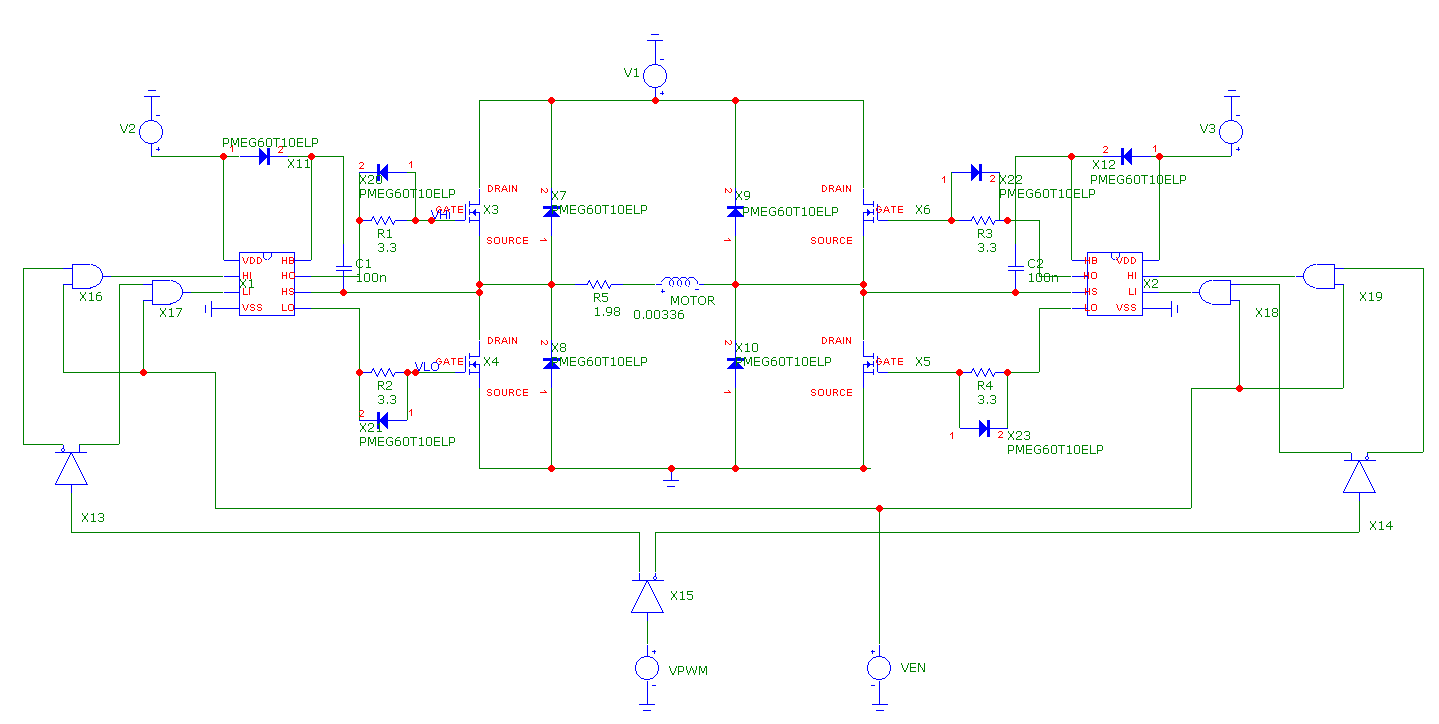

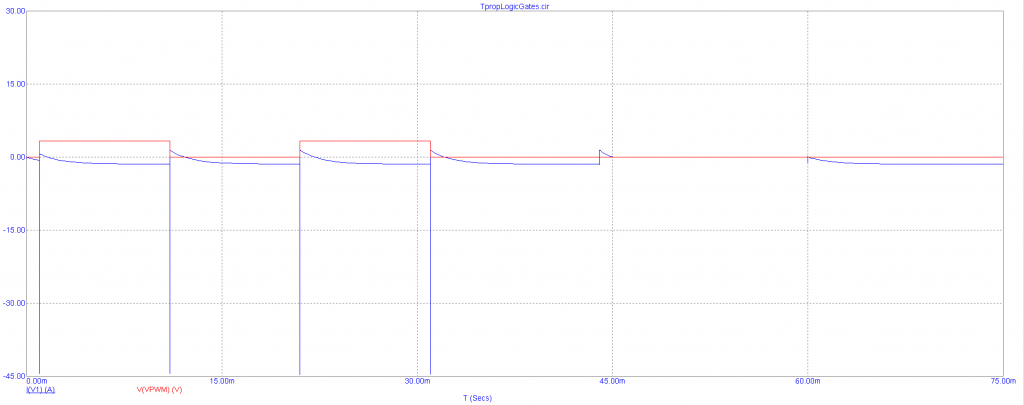

I’ve also run a new simulation of the H-bridge, with diodes placed at the MOSFET gates to speed up turn-off times and hopefully prevent shoot-through:

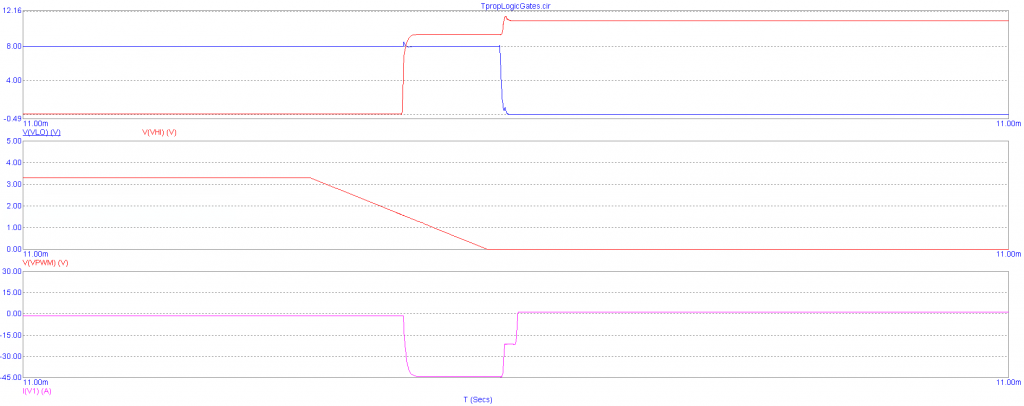

Unfortunately, simply placing the diodes there does little to prevent shoot-through, as can be seen in this simulation of the power supply current (the blue waveform) as the H-bridge is switched:

Clearly, there are immense current spikes exceeding 45A in amplitude as the motor controller PWM input is turned on and off. Simulating for the gate voltages of the hi and low-side MOSFETs on the “left” side of the H-bridge confirms that these spikes are caused by shoot-through:

The voltage at the MOSFET gates (the top set of waveforms) is high for both hi-side and lo-side MOSFETs for a short amount of time, causing the MOSFETs to short the supply to ground temporarily.

I’m behind by a week. I resolved to complete the motor controller board by the first half of this week, but was delayed by a series of unfortunate events (design report due on Monday, design review for another class, and an Open House event for prospective grad students). To catch up, I’ll need to resolve the shoot-through issues in simulation (hopefully through simply finding a circuit to copy-paste). Then, I’ll need to wrestle with the MOSFET footprints and find a way to position them so as to avoid adding extreme amounts of parasitic inductance into the gate driver traces. Lastly, I’ll need to talk with Kenny about what the circuitry for the test-setup should look like (so that he can do the actual design by himself, and perform sanity checks against our general expectations).

Next week, I hope to complete the layout for the motor controller board, and meet with one of the professors to perform a design review (probably in the latter half of the week). Given the challenges that this part of the project has posed thus far, I think that’s the most I can hope for.