Yay! Last status report!

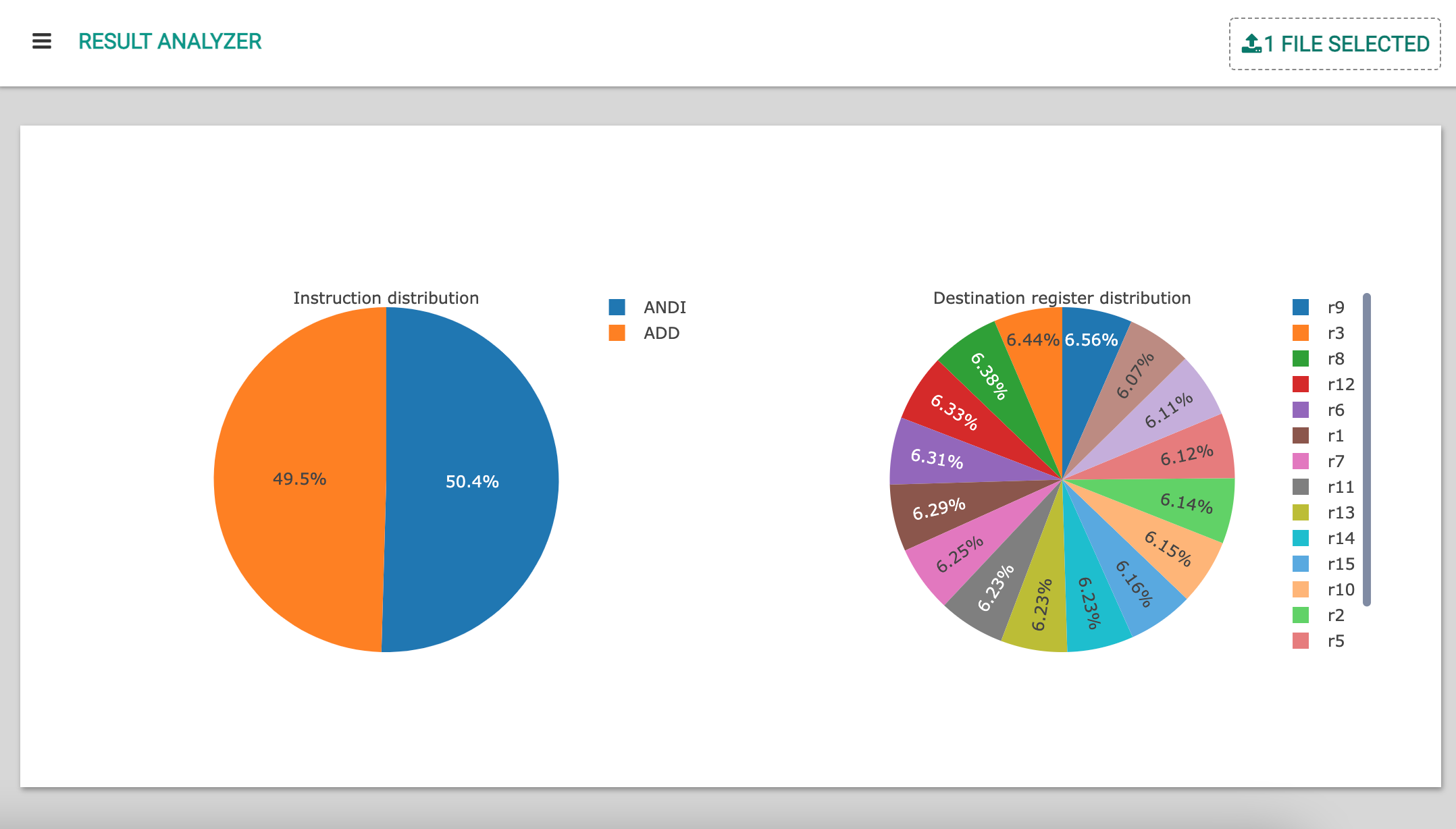

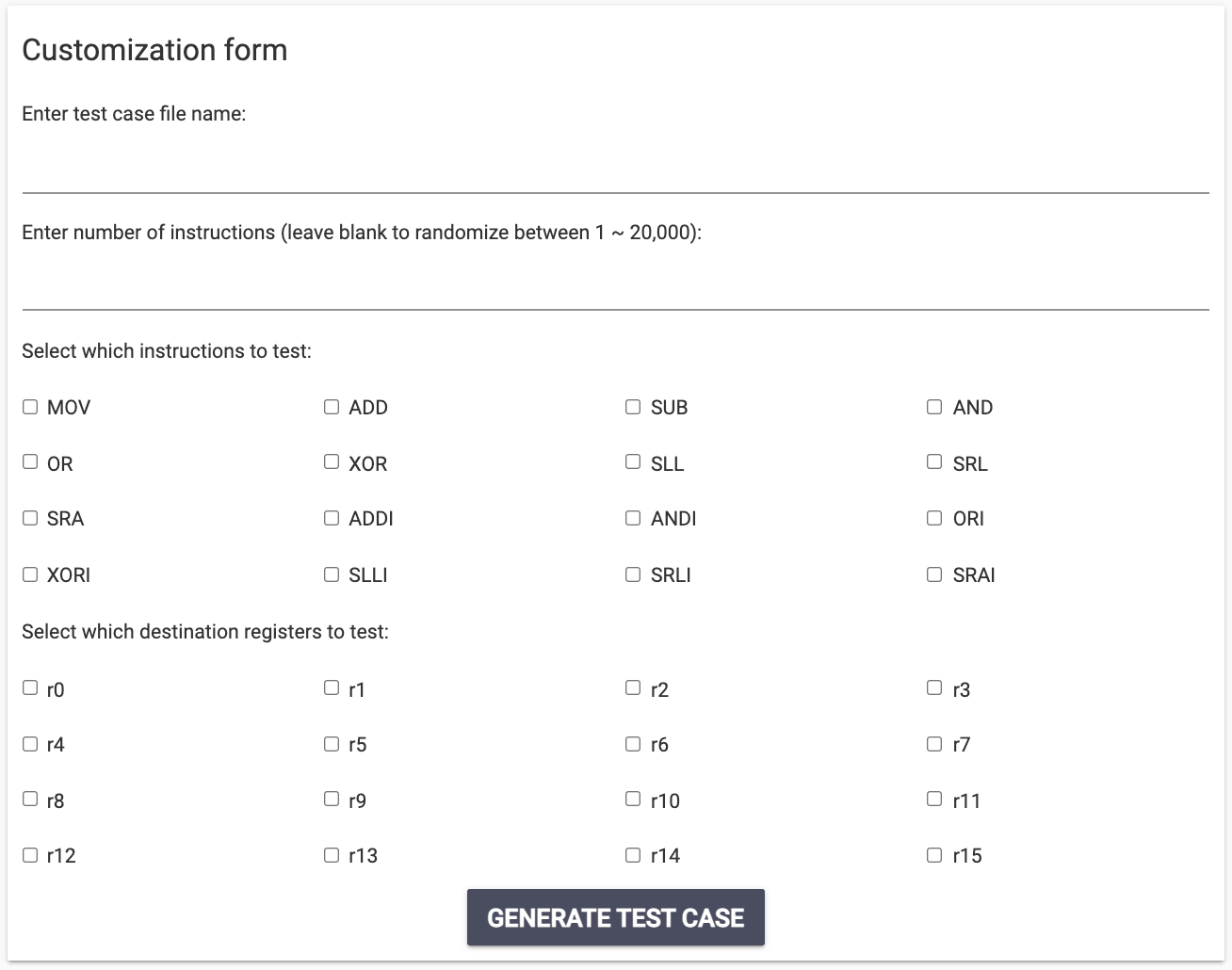

For the past two weeks, I worked on a few different tasks. During the week of Thanksgiving, I finished our input GUI (below is a screenshot). I also worked on the final presentation slides and practiced delivery, given that I was the presenter for our team this time. This past week, I practiced the presentation more and am beginning to work on integration. More specifically, I need to update the output comparator to accept a slightly different file format that Grace and Ali are working on sending from the FPGA.

I am on schedule. I’m at a point where I’m essentially done with all of my individual tasks for the semester. During this final stretch, I’ll work with my teammates on integration, more testing, plus the final deliverables.

To Tamal and Joel, thank you for your help throughout the semester 🙂 See you at our demo!