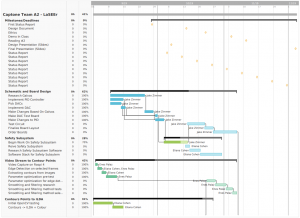

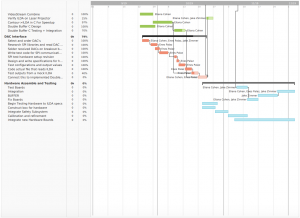

Week of 10/19/2019

Enes Palaz Status Update

- What did you personally accomplish this week on the project?

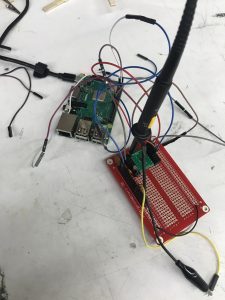

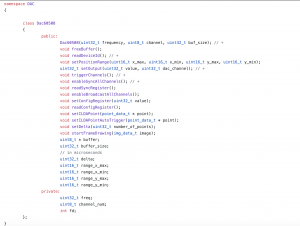

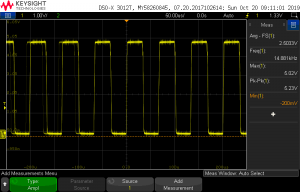

This week I completed designing and coding the DAC controller. Test setup for the code can be seen below. A screenshot of header file with function definitions can also be seen in the second image posted below. A screeshot of oscilloscope readings of a square wave generated is added too in which we tested the proper communication speed to get 12,000 points per second. Currently, I am still testing it to verify our timing constraints are satisfied and triggers happen simultaneously.

- Is your progress on schedule or behind? If you are behind, what actions will be taken to catch up to the project schedule?

My progress is behind by 2 days because of the problems that I had while testing my code. Fortunately, I was able to debug my code to make it work properly. So, my schedule for DAC is moved by 2 days since I needed 2 more days of testing. This will push our integration with double buffer by 2 days. We have enough time to move integration by 2 days but I will try to spend more time on integration to finish it earlier than what we planned for.

- What deliverables do you hope to complete in the next week?

My deliverables for next is the integration of double buffer and DAC control system that will read from double buffer and automatically draw a test set of frames and points.

Jake Zimmer Status Update

- What did you personally accomplish this week on the project?

- I got familiar with the STM32 development environment. The IDE is essentially a reskinned Eclipse IDE with some really near extra features like pin feature configuration. The SDK has some really neat features that make me confident that this was a good choice of microcontrolller and make me want to use it in future projects.

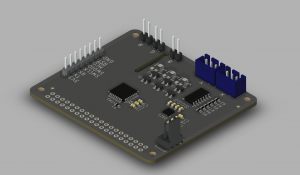

- I finished the board design and routing and the schematic is currently under review by Elliana. The finished layout can be seen below:

Board Design

- Is your progress on schedule or behind? If you are behind, what actions will be taken to catch up to the project schedule?

- It is a little behind due to needing to coordinate schedules during this busy time of year in order to do the schematic review. To rectify this, Eliana and I decided to simply have her review the board without myself present.

- What deliverables do you hope to complete in the next week?

- Next week I hope to finally order the boards and have some of the code running on a dev board. The boards should arrive within two weeks but I will develop the firmware in parallel as to mitigate delays.

Eliana Cohen Status Update

- What did you personally accomplish this week on the project?

-

- Began reviewing Jake’s schematic designs

- Further improved speed conversion time of OpenCV images by distributing the image conversion into multiple threads

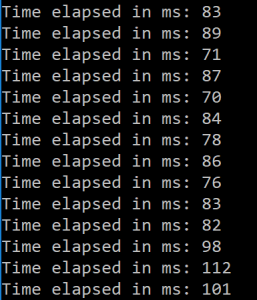

- Updated speed conversion time to include time to interface with camera [From around 250ms conversion time to 70-120ms conversion time, the differences are due to number of features in a frame, which will be capped at 1.2k points allowing us to reach our under 100ms conversion time goal.]

- Is your progress on schedule or behind? If you are behind, what actions will be taken to catch up to the project schedule?

A little behind due to preparing for exams, most of this work has been accomplished over the 3-day weekend. I should be back on track after focusing on finishing up more image optimizations and ready to test out the hardware next week.

- What deliverables do you hope to complete in the next week?

By next week, I should have completed:

- Work with Enes to test out ILDA images on the DAC systems

- Test DAC board with laser systems

- Work on integrating with Enes’ software

Team Status Update

- What are the most significant risks that could jeopardize the success of the project? How are these risks being managed? What contingency plans are ready?

Image Processing time is still a major risk, and there are risks with producing our circuit boards in that the boards may have some minor design errors. These are being mitigated through reviews, and also the ability to ‘botch wire’ boards to fix minor mistakes. The time for this is already planned into our schedule, so that we have time to fix our boards. We’re also working on integrating the systems together this next week so that we have more time to fix integration problems as they arise.

- Were any changes made to the existing design of the system (requirements, block diagram, system spec, etc)? Why was this change necessary, what costs does the change incur, and how will these costs be mitigated going forward?

No new changes.

- Provide an updated schedule if changes have occurred.