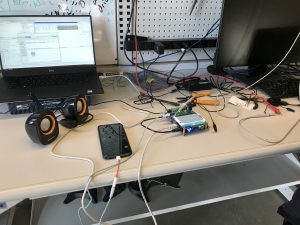

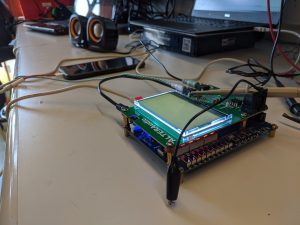

This week was primarily towards getting audio pass through working for the demo next week. Along with the general debugging that all of us had to do, I was in charge of setting up the basic verilog to drive the necessary clocks and pass the adc output to the dac.

To summarize: System Clock (25 Mhz), B Clock (3.125 Mhz), Word Clock (48.8 Khz)

Each of these were driven to the corresponding GPIO pins on the FPGA to properly control and configure the IC chips.

There were initial problems of the values not driving on the correct pins but this was due to the indexing bits in verilog being different than the actual physical pin.