This week largely saw a return to a more normal work schedule, and beginning to act on the updated plan.

Our new timeline to account for the recent changes is shown below:

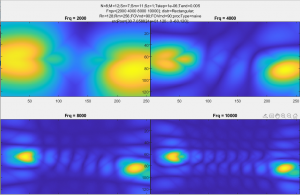

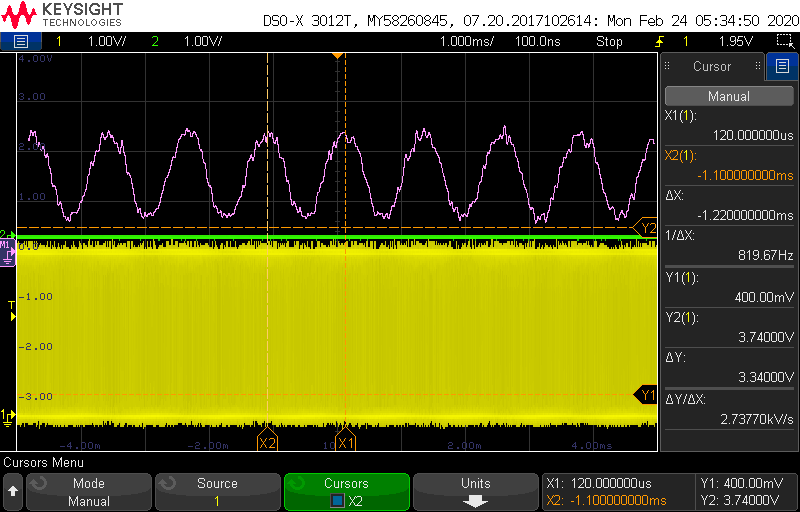

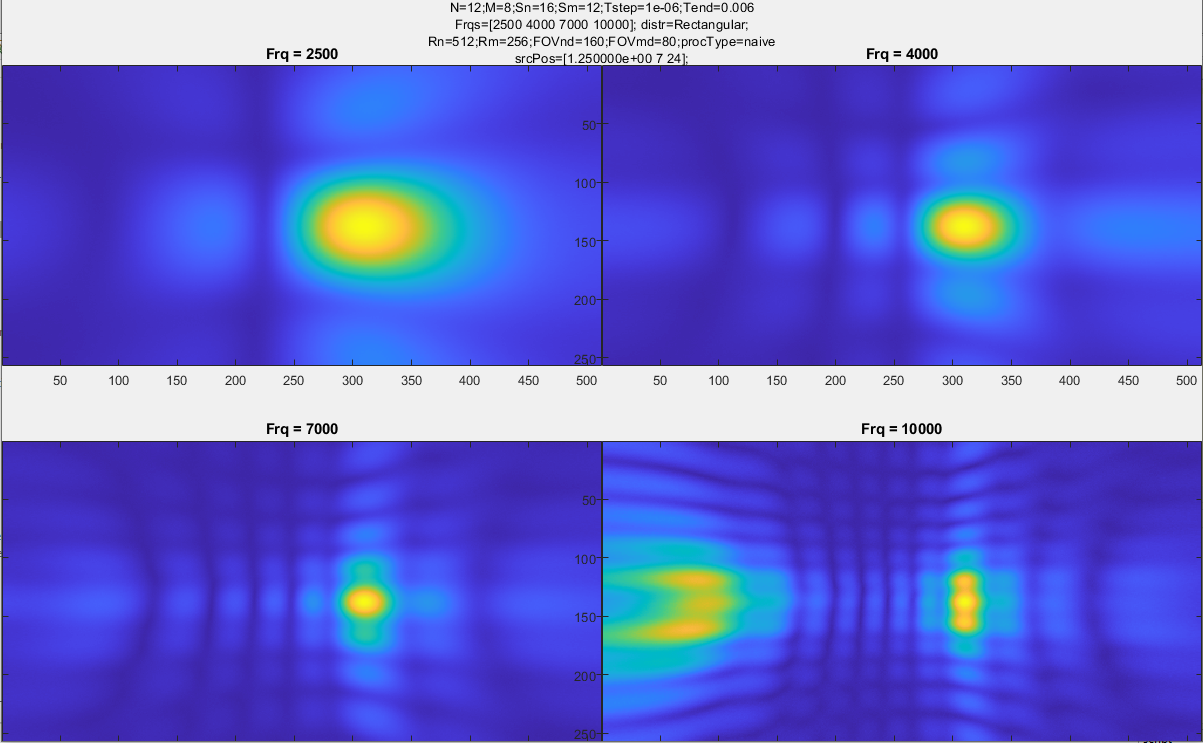

Most components are on track or completed, though there are several components which have fallen slightly behind. Mainly the computer-side driver to receive and decode data from the FPGA, and the array processing software. To help get back on track, and since much of the audio calibration/testing has been removed from the scope of the project, Ryan has become more involved with the software/processing side. John also plans to finish the network driver this weekend.

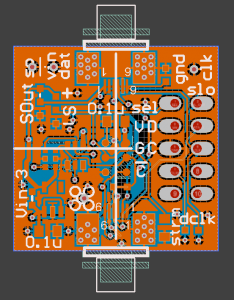

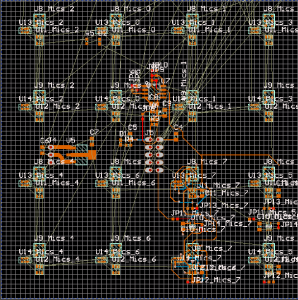

On the hardware side, the architecture of the physical architecture was slightly changed to simplify the design. Specifically, from having a single carrier board with connectors for each microphone element, to having a small number of boards with many microphones each, that connect directly to the FPGA board using ribbon cables.

Our risk management has largely been reduced the last few weeks, as most of the main risks we foresaw were eliminated over the course of the project so far, or, did not end up being issues. Our PCB and digikey orders have been fulfilled already, so unless there are problems with shipping, we should have the necessary hardware. If there are any problems, board design includes several generic alternatives for each critical part, so as long as at least one supplier remains open, we should be able to finish the hardware (see John’s update for more details). On the software side, risks and mitigations have not changed.