All of the changes to daily life this week didn’t leave much time for work on capstone outside of class, so the additional work completed has been minimal.

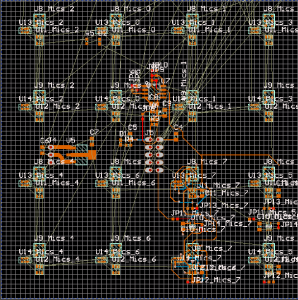

Most of what I was able to work on this week was design of the microphone array boards, which was originally scheduled to be finished over the last couple days of Spring Break.

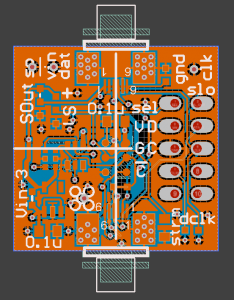

I was able to complete a simple breakout for the microphones, as we’d originally planned to have an array where each element is identical, and on its own small carrier board, with the boards connected to the FPGA with FFC cables.

However, with the changes to the project, I decided this was probably too work intensive to build for a single person to complete, and, difficult to build without the tools we expected to have available.

Instead, the design was changed to a set of 6 boards, each with 16 elements, and a single connector to the FPGA. This board is still in progress.

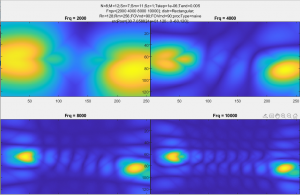

This cuts down the total number of components needed significantly, and reduces the number of connectors from about 200 to just six. The drawback is configurability, if we later find that the 1″x1″ array spacing does not work well, there is not much path to changing it, some workaround would have to be found. All of the analysis so far has indicated that 1×1 is close to optimal for the frequencies we’ve chosen, but, practical testing will undoubtedly find problems that simulation did not account for.

I have done some analysis of possible workarounds to changing array geometry, mostly pertaining to moving the sub-arrays slightly off-grid relative to each other (so, for example, two array are placed with their nearest elements just 0.5″ apart instead of 1″), which does allow for aliasing and other artifacts to be traded off with directivity, though the tradeoff is often steep in whatever is being traded against (i.e. to gain a little directivity, you have to tolerate significant artifacts, and vis versa). Hopefully we will not have to do any of this, and all the analysis so far says we won’t, but it is good to know roughly what we’re facing if we do have to.

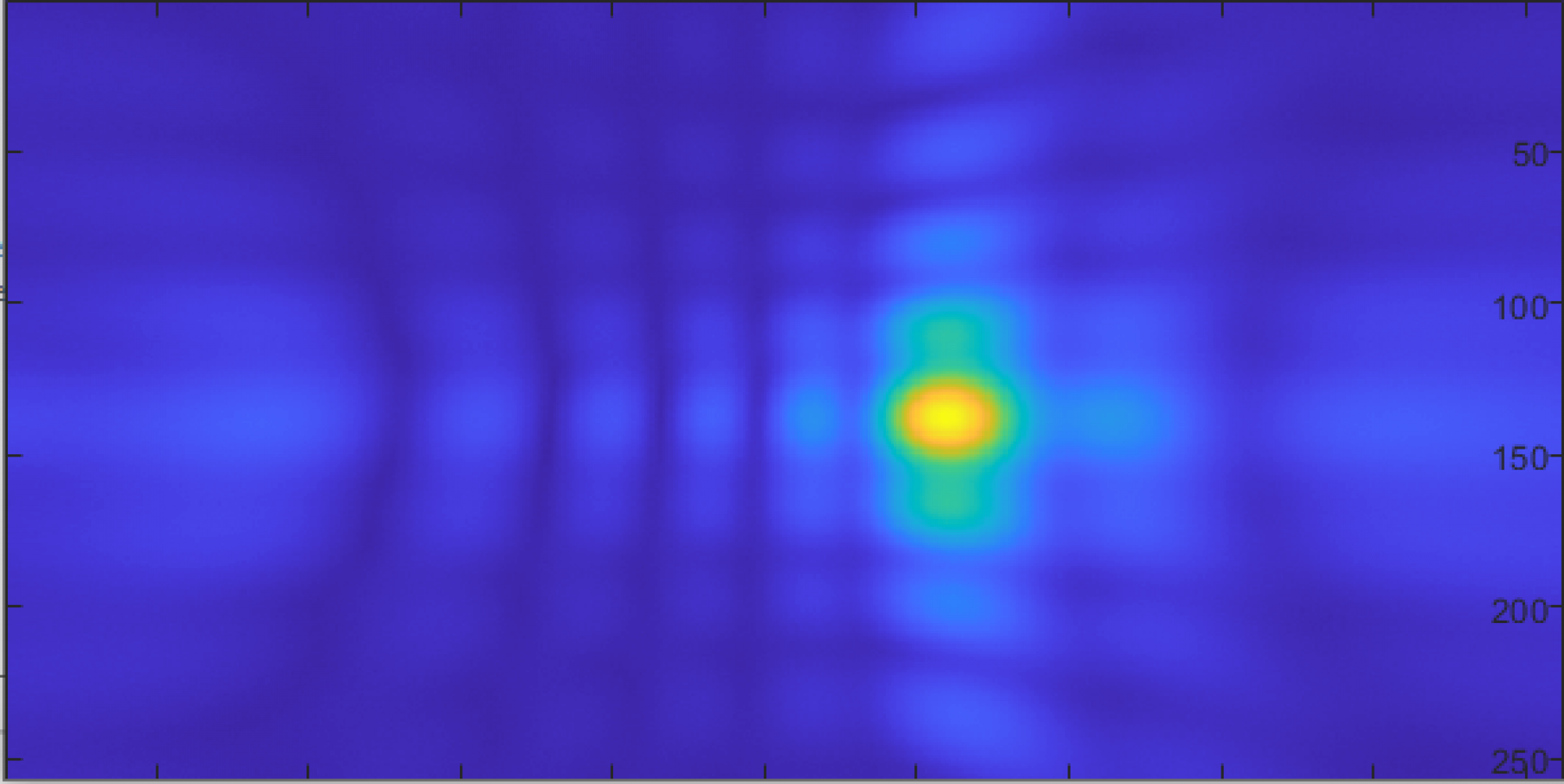

Photo shows some of the strange artifacts that emerge with unevenly spacing sub-arrays. The two sources are real sources, so the array is not aliasing, but the sources are no longer round, they are shaped strangely, and, not exactly the same. The output is still usable, but this illustrates a significant tradeoff of this method of constructing the array.