This week didn’t bring us any new risks. As with last week, there are areas of our design that still need to be fleshed out, and they could present unforeseen roadblocks later on. In order to minimize this risk, we will produce a detailed design report that explores all of these possibilities in the next week and a half.

We’ve been working on the deisgn report and that is uncovering some of the stuff we still need to think about. For example the assembler pipeline, the software demo, and the details of the components (i.e. multipliers and dividers). However we have no new big changes to our schedule this week.

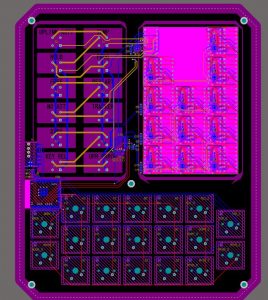

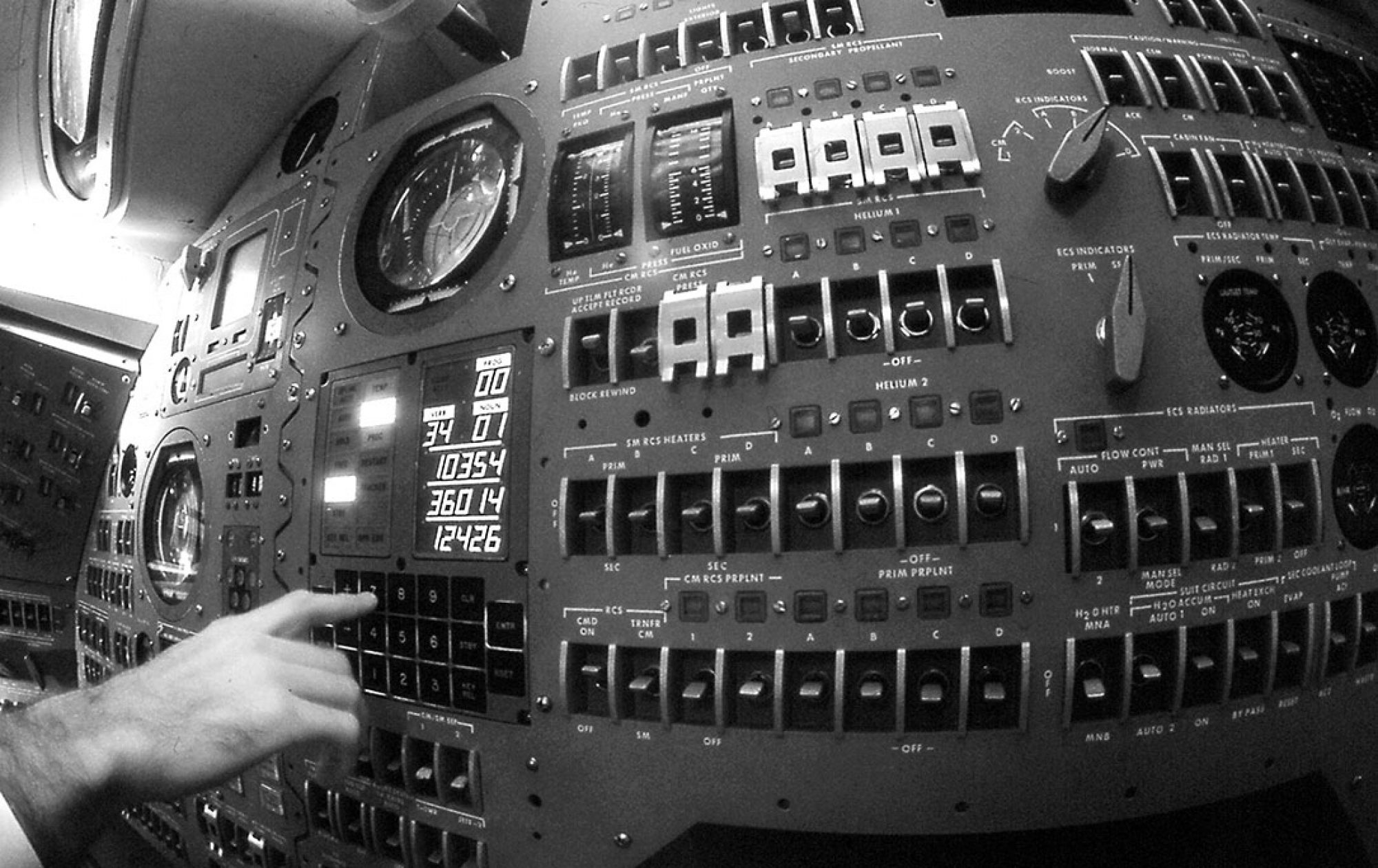

After we presented, we talked with our TA about potential risks and mitigations. We came up with basic high level attributes, such as: If the PCB has errors, bodge wires will be used to discretely fix the traces. If the worst happens and the PCB goes up in flames, then we will opt for a software DSKY demo. If our critical path is longer than 200ms, we will weigh the cost/benefits of spending more time optimizing or opting for a slower clock. If some of non-essential instructions are costing us too much time/effort, we will descope them if necessary. Finally, if we are running out of time, we will focus on creating a simple but compact demo that demonstrates the absolute key features of the DSKY.