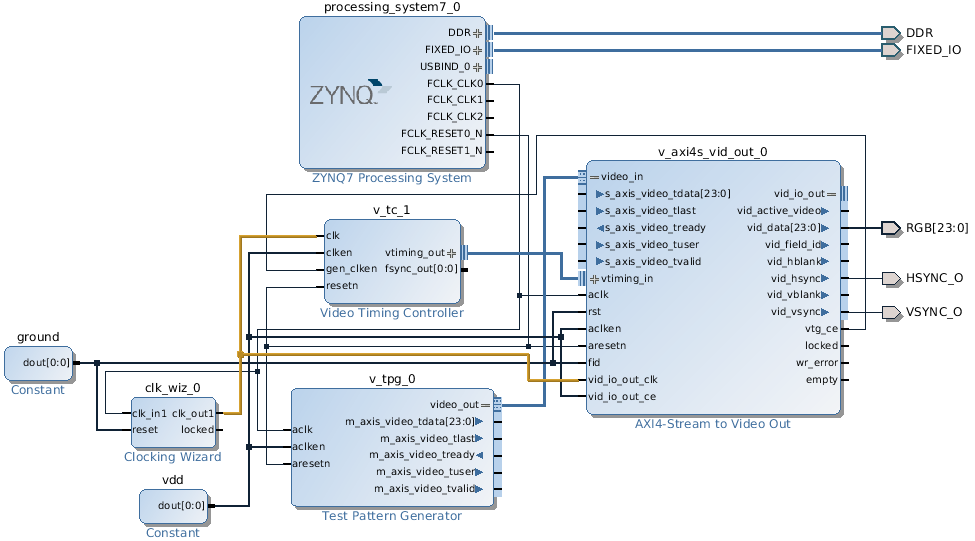

This week I gave up on the HDMI pipeline on the pynq zynq board. After 3 weeks of trying, I couldn’t get a successful toolchain for the board working. The Pynq (also sold as the Arty Z7 board) was discontinued, and no support exists after petalinux 2017, meaning we need to use archived tools that no longer work on modern linux versions. Additionally, the hdmi pipeline was finicky and required regenerating the bitstream and rebuilding the linux image to change resolutions. This process takes several hours, and we were unable to successfully get the pynq to recognize an hdmi display and output data.

Switching to the ultra96 board meant we could make use of the UltraScale+ Zynq’s hardware GPU and skip the complex design of an framebuffer/hdmi pipeline. Since switching, we’ve already brought up hdmi and i2c drivers on the ps system, and built bitstreams and petalinux images. I successfully wrote a driver to interface with the knobs over i2c, and have been working on deploying Qt to the ultra96 to build the gui. So far, I’ve successfully configured petalinux to include Qt binaries, but building the Qt binaries has already taken multiple hours and might be an overnight process.

This week I’m hoping to deploy the Qt gui to the ultra96 and a write user-space drivers for Graham’s AXI peripheral work.