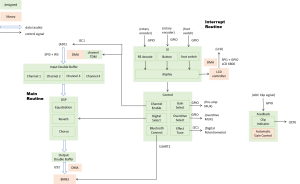

This week I have finalized the microcontroller block diagram, though we had several component/interfaces changes this week and there were several intermediate versions. The microcontroller design document is also updated accordingly.

Microcontroller Program Design_0306

I have setup the STM32CubeIDE environment for developing the stm32f4 board, and looked at the examples and tools for setting up pins, controlling interrupts, etc..

I had made some feasibility studies including:

- Multiplexing 4 audio inputs at the same time. I made sure the ADC we use have TDM output capabilities, and though our board itself does not have software support for TDM protocol, with SPI interface we could read the data line in order, and get the 4 channels in order.

- Using DMA for frequent and high bandwidth data transfers. I confirmed that DMA can support audio input through SPI, output through I2S, and LCD output through SPI.

- Only using SRAM for DSP runtime data. I studied the flash on stm32 board and know that the endurance and latency of flash writes make it infeasible. So our run-time writable memory is confirmed to be only SRAM. (Sam will also mention this)

I did not finish defining all the interfaces and headers in program, because we had several component and interface changes which lead to overall software design change. There will hopefully be no more changes in the future and I will finish the following next week:

define code interfaces/function prototypes; test some of the protocols on the discovery board (I2C, SPI, UART).