Status report is a bit late, isn’t it? Turns out reports aren’t due the day before returning to the lab.

Accomplishments

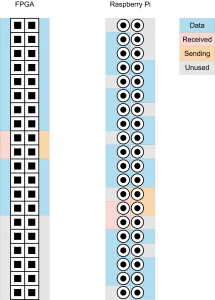

For the past week, I’ve been detailing the protocol for the physical connection between the FPGA and the accompanying Raspberry Pi. The protocol accounts for available GPIO on both devices and attempts to maximize throughput from the Pi to the FPGA.

The document detailing the physical setup is here:

https://drive.google.com/open?id=12h_0X_CB3D_IyGUgf5_b_YGxSVW09nrvIl3oF7lknj8

The core supplemental diagram illustrates the GPIO on each board:

This design uses every GPIO pin on the Raspberry Pi. For convenience, The data pins are joined by direction, split across the send/receive notification pins.

Schedule

This week has a lot riding behind it: according to our Gantt chart, this week we determine if our ethernet implementation is viable. To test this , I need to mess with the DE2-115 boards and get an echo server running over GPIO. This server is likely going to form the backbone of our communication with the FPGA, as we’re limiting the effectiveness of the RPi to act as an alternative Ethernet PHY board. If all goes well, I’ll have something to write about. If all doesn’t go well, I’ll have something to write about.