Team Status Report

RISKS

Our greatest risk at the moment is the lack of time to integrate the software and hardware systems of our project. In particular we recognize that there are only 5 weeks to implement and test the entire system. Since each team members’ roles are distinct, we feel like each component of the system may be built and tested in time, but putting them together might need a little more time.

The risk stems from our schedule being pushed back due to our iterations in project focus (see last week). We have spent too much time trying to conceptualize our project. Therefore in order to eliminate the aforementioned risk, we plan to cut back on research time from 2 weeks to 1 week in order to ensure time for implementation and testing.

DESIGN CHANGES

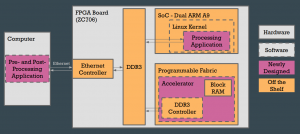

We have come up with a design for our entire system now.

We also decided to add a testing suite to our design, since our goals for the project include developing a testing framework to verify the output of our algorithm.

UPDATED SCHEDULE

Our updated schedule has detailed task divisions amongst the group members. Maxwell and John will be focusing on the hardware component including the SoC, and Riki will be focusing on the software application and the testing framework.

Maxwell Johnson

Personal work:

This week, I designed the architecture and many of the hardware specifications of our project. This required research into the functional capabilities of our FPGA board (a Zynq 7045). On of the areas of research was how to connect to an external computer. Ethernet is the most plausible, based on the high bandwidth (up to 1 Gbps) and the fact that Xilinx provides an IP block for interfacing with the ethernet controller. A concrete result of my research was our block diagram, which is shown above.

I also modeled the demands of our application in terms of the resources on the programmable fabric. To do so I designed a prototype of a hardware energy filter module and synthesized it in Vivado for our board. The unit used 89 LUTs, 48 flip-flops, and 1 DSP unit (used for multiplication). The utilization report can be found here: test_unit_utilization_synth.txt

The limiting reactant is the DSP units—our board has 900 DSP units, and hundreds of thousands of LUTs and flip-flops. 900 DSP units align fairly well with the horizontal resolution of the video we want to target, 640 pixels. This leaves some extras, which can be used for other areas of our design. Leaving some units unused will also make routing easier which will keep our clock frequency low. In the most complete version of the algorithm, we would have to compute 9 pixel differences—1 per direction (X, Y, time) per color (red, green, blue). Each difference takes one cycle (again limited by DSP units), so we can process one row of one frame per 9 cycles. At 50 MHz, this design will be able to process 17k frames per second.

Progress:

Our project is coming out of a couple weeks of turmoil. We have spent most of our time readjusting our project’s course, talking with the various new faculty we’re working with, and defining our project. This week, I was finally able to start working on some design. My deliverables from last week were to synthesize a test sketch in Vivado, to upload it to our board, and to begin learning the toolchain for SoC development. After another round of readjustment, John was assigned to work on the SoC; however, I succeeded in creating a test of our functional units and synthesizing them in Vivado, as mentioned above. Our project has changed direction since last week, but I feel that our work this week has put us back on schedule.

Deliverables:

This week, my main task is to finish the design report. This will require more research into the capabilities of our board as well as the demands of the applications. At some point during the week, I hope to instantiate the DDR3 controller IP and interface between the programmable fabric and the board’s main memory.

John Zhang

Riki Khorana

This week I was contributing to the project redirection, and the design proposal slides. On the technical side of things, I was preparing for the software environment by installing OpenCV for C++ and researching testing methods.

My progress is still on schedule, although I will have to speed things up to get my research done soon.

My deliverable for next week would be completing the software research on seam carving algorithms and video evaluation techniques so I can start implementing the whole system the following week.