This week was continuing to test the panning and bit crushing modules in simulation as well as in the python model. Additionally development/testing for the adc module is ongoing and development for the dac module.

The gathered specs for the adc model are listed below:

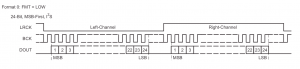

ADC Translator

Master clock = 25 MHz

B Clock = 32 clocks for left, 32 clocks for right (3.125 MHz)

Word Select = left channel (0) right channel (1)

Dout = comes left channel (MSB – LSB) and right channel (MSB – LSB)

So I have been working on changing this spec to actual rtl. The rtl consists of an audio buffer that is 32 bits wide (2 channels). Out of these 32 bits only 24 are valid and from those 24 we are only using 16 bits for our DSP. After every two audio frames (2 channels) then a valid is asserted for the next DSP block to latch the audio data. From here a new buffer starts to be created with the new audio values. Additionally the B clock is 25 Mhz divided by 8 which is implemented with a simple counter.

On another note in simulation we started to hear what sample audio sounds like in 8 bit mode. The result seems to be very noisy with the current example because those 8 bits seemed to have carried a lot of the audio info. Looking online we may need to normalize the audio to make this a useful effect.