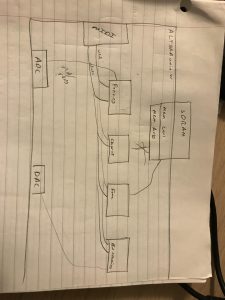

This week was continuing to come up with a concrete plan for how to structure the verilog code base.

This was just a rough sketch done in lab, but through the discussion we organized all of the major modules required for the integration phase.

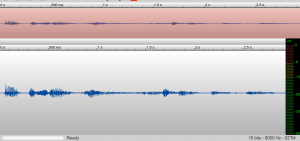

The panning module was written and I started testing and verifying the module. Based on a discussion with the rest of the team and Professor Nace we realized that having some sort of testbench that can use example wav files for the generated data and sending it through the DSP modules will be an efficient way of testing. At the same time we can ensure that our algorithms are correct from a auditory perspective by playing back these wav files and making sure that the sound played is the effect we expected.

This is an example wav file that I have been using for testing purposes. I have written python code that allows us to read the data (stereo) by each audio frame. The plan is to then dump these values into some sort of systemverilog array file so that we can instantiate a driver to read and drive these values into our module for testing purposes.