Integration is finishing up both with the host and with the data pipeline router.

Host to Bus

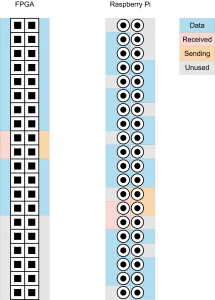

With the host using UDP only for the finder, the Pi has both a UDP server for being found and a TCP server for receiving data. The TCP server follows RCE-style order, where every sent command is followed by a response. The host prepends the length of the message, so that the Pi and bus can detect the length at the start of the command.

Bus to Hardware

TJ gave me the code to the memory model. The bus morphs this into streaming an incoming command, where instead of waiting for read enable, it raises “done” every time a command is received. As the hardware is in charge of copying commands to an assigned location, the hardware keeps up with the bus.

Integration needs to be solidified with the host and I am in contact with TJ to help him complete hardware integration.