At the moment, the most jeopardizing issue we have is figuring out how to integrate everything into one package on the board including a display output. As our efforts have been focused on building and accelerating the fluid simulator, we are still unsure about display. We have a variety of backup plans for this issue issue, such as producing a file of the rendered output, and producing the display from somewhere else. This still aligns with our project goals as we are not aiming for a real-time system, and are just trying to accelerate the fluid simulation process.

We decided to make a system change, such that the FPGA platform will only perform the fluid simulation algorithm. In other words, it will take an array of 3D positions and output an array of 3D positions for each frame, and save that to a file such that a host computer that is able to run Scotty3D can load in the simulation file and play the fluid simulation. This system change plays into the category of “request scheduler”, which is shown below.

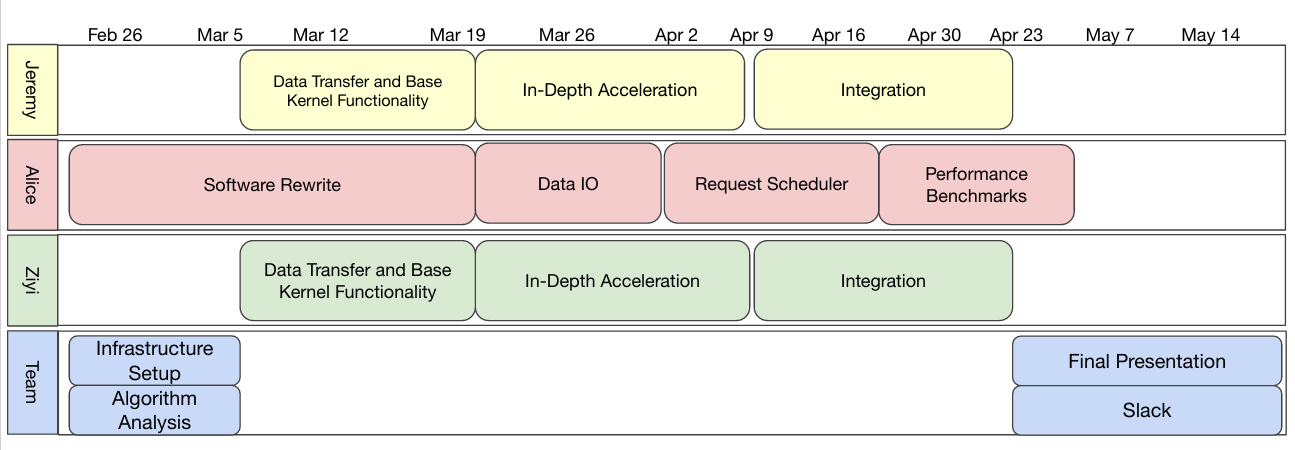

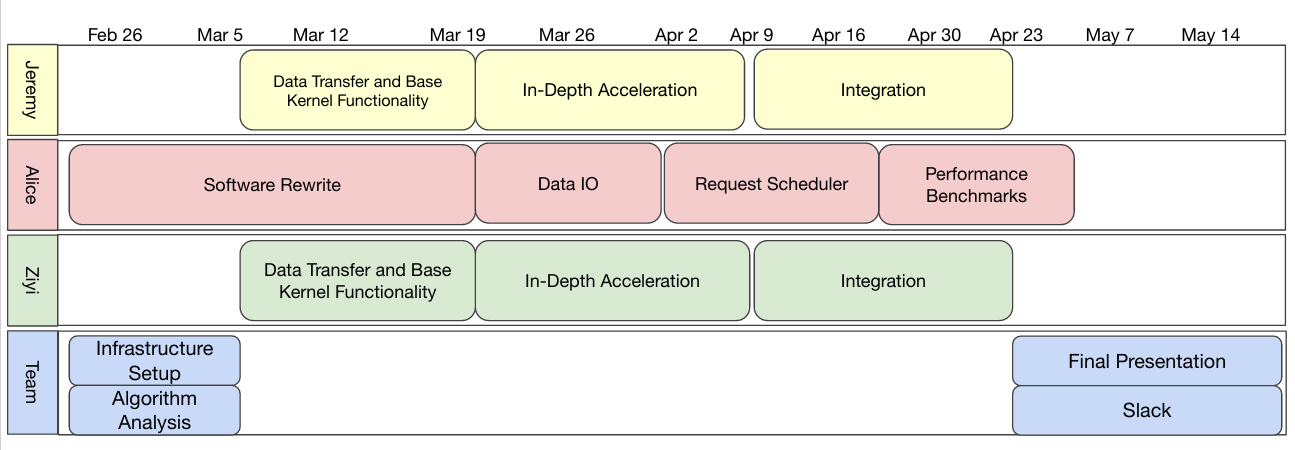

Jeremy and Alice also swapped responsibilities since Jeremy is more experienced at C++ and digital hardware, and Alice’s knowledge of the Scotty3D codebase is helpful for adding additional features necessary to load the simulation into Scotty3D and getting the FPGA to send over the necessary data to the host computer. Below is the updated Gantt Chart: