This week we got a ton done on the hardware side of things. First of all, after finally squeezing out the final few compilation errors, we managed to get a trimmed down version of the kernel (everything sans nearest neighbor loops) built using Vitis HLS synthesis. After looking at the synthesis analysis, we were able to see that the correct loops were also getting synthesized, which meant that our code was being inferred correctly.

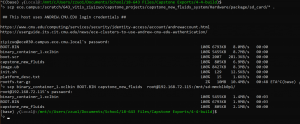

After passing synthesis, we were able to export the rtl implementation (the .xo file) and import it into regular Vitis itself without any additional troubles. Then, after implementing some basic interfacing code between the host program and the kernel, were were able to build a binary to run on the FPGA. In order to get this binary onto the board, we simply scp’d the files onto the board.

Running the program resulted in a segmentation fault, so we still have a bit to go. My goal for next week is to debug the interface and work on some optimizations with Alice and Jeremy.