Individual updates

-

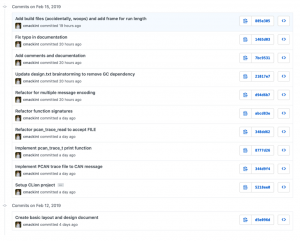

Continued firmware bringup efforts that started in late January:

-

Worked with Deepak Pallerla and other CMR members to refine CAN, ADC, and GPIO drivers and their respective interfaces

-

SPI via DMA implemented and tested (below, left)

-

-

Designed high-level TOM system architecture by outlining required tasks and synchronization objects, including the radio API

-

Implemented and tested synchronized full-duplex SPI interface proof-of-concept

Schedule status

I am currently on schedule for my assigned tasks. Radio API design was at risk of falling behind due to missing XBee hardware earlier in the week, but they have since been sourced; I will have enough spare time this weekend to test out various configuration details.

Deliverables for 2019 Feb. 23

-

UART drivers brought up and tested

-

Radio API tested with XBee

-

Various Wi-Fi configuration/connection details must be ironed out

-

Full-duplex must be tested for robustness

-

-

XBee range tested