Significant risks and risk management:

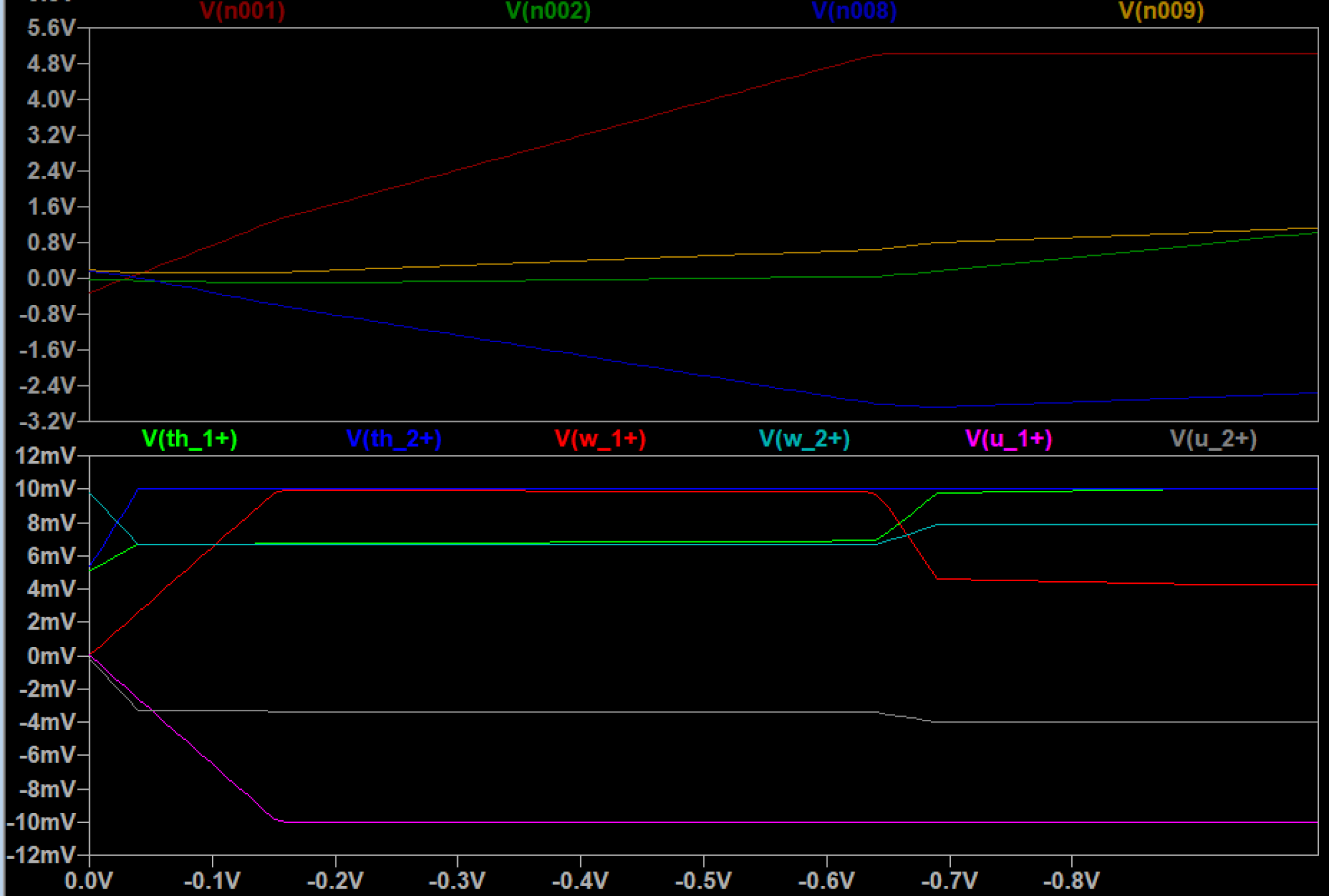

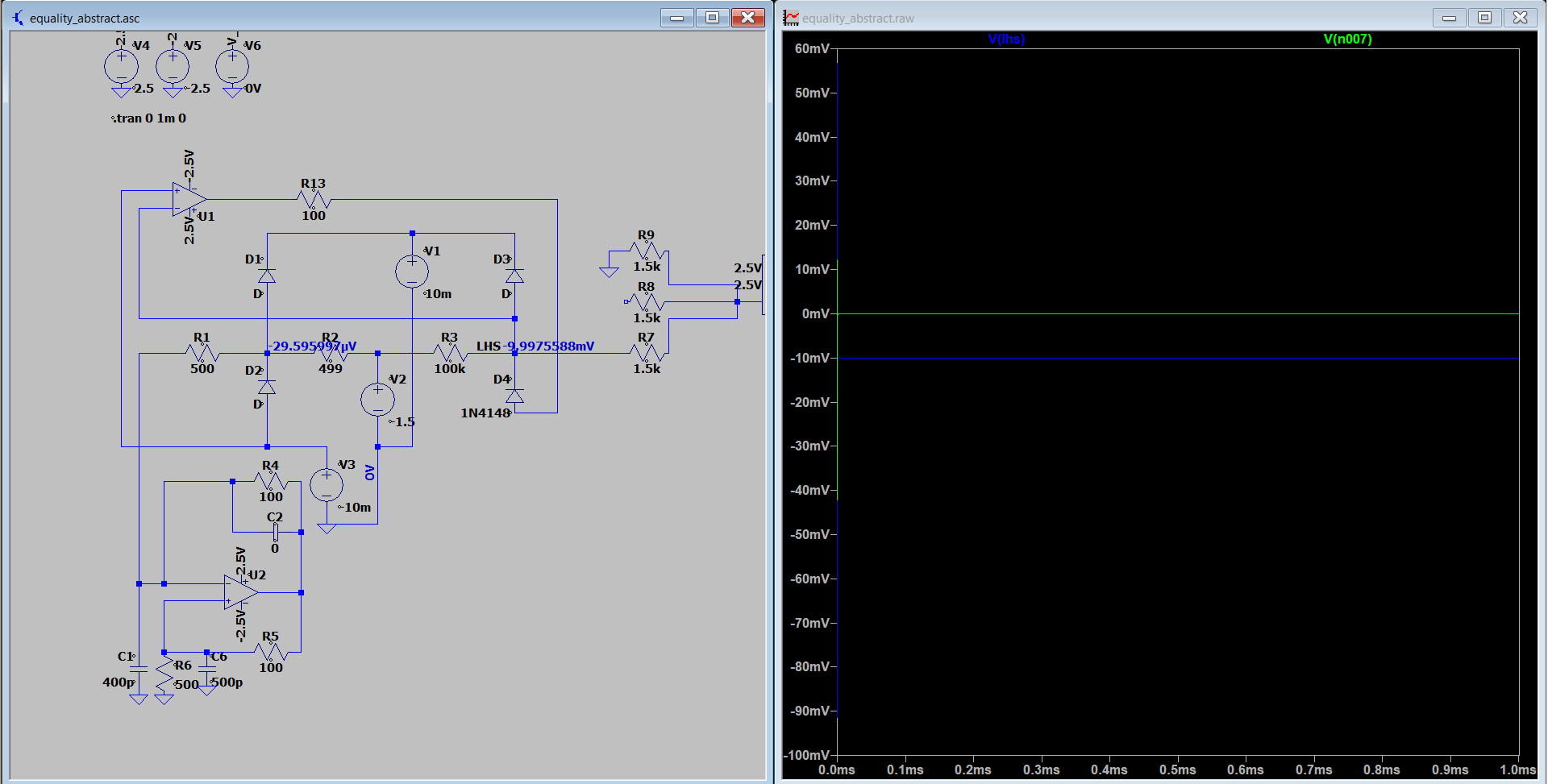

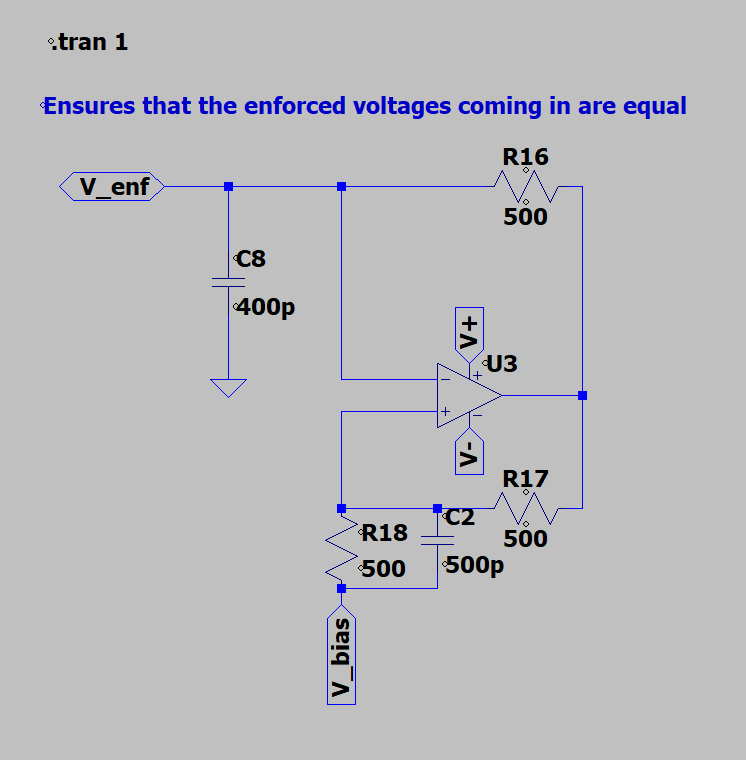

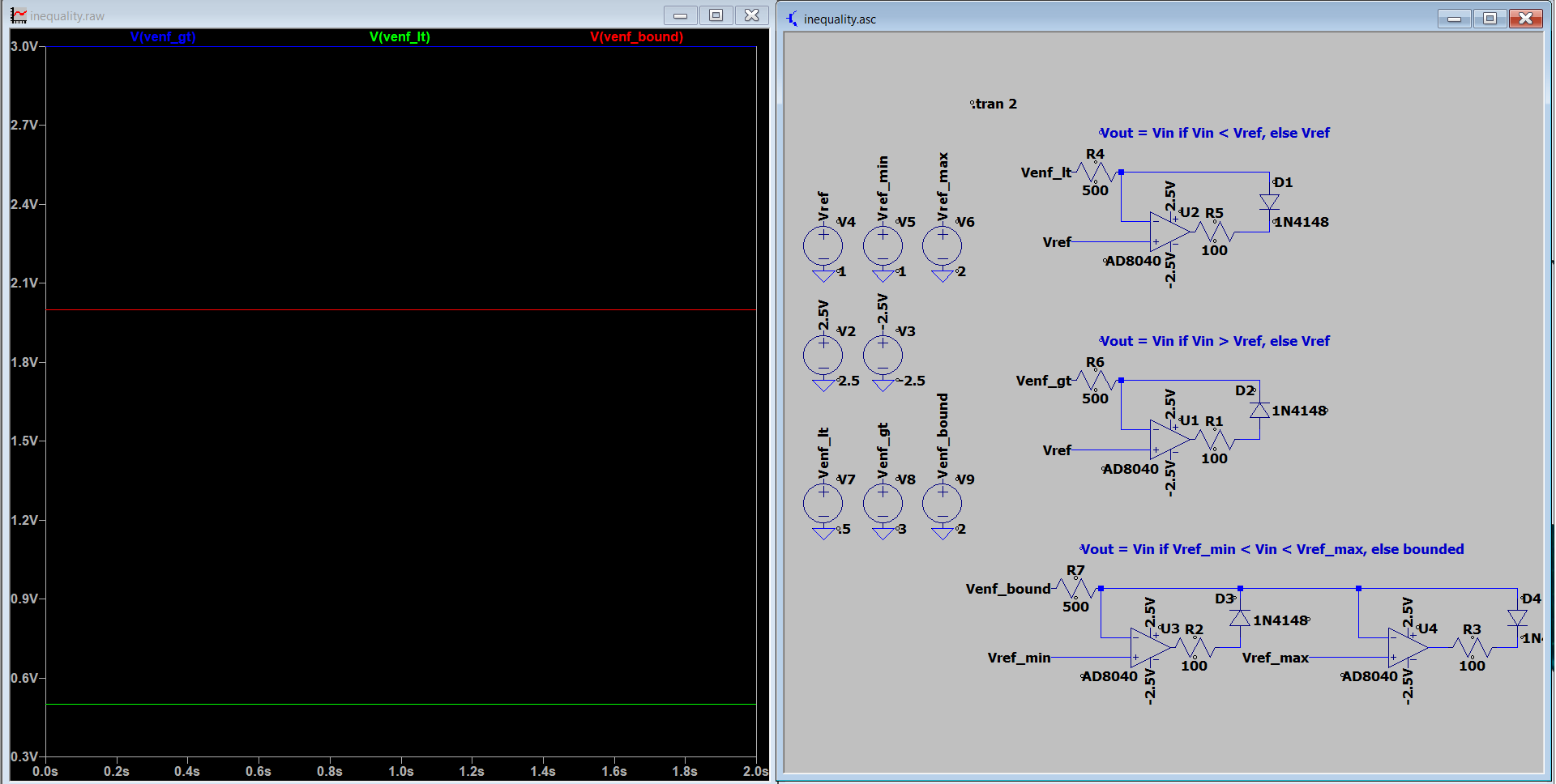

Risk: Dr. Vichik’s analog circuit failing to solve the problems we specify

Description: In a preliminary circuit simulation, we tried to solve a simple LP with the analog circuit proposed by Dr. Vichik. However, we found that the circuit fails to solve the LP with certain parameters. This indicates a risk that the circuit might not be able to solve the problems we specify.

Severity: If Dr. Vichik’s circuit fails to solve optimization problems we specify, the progress of the whole project would be severely jeopardized, because the design of our analog SQP solver is centered around Dr. Vichik’s circuit primitives. This is the most significant risk we’ve encountered so far.

Resolution: We are currently investigating the nature of the issue that causes Dr. Vichik’s circuit to fail. We aim to either solve this issue by improving Dr. Vichik’s design, or mitigate it by avoiding the optimization problems that would cause it to fail.

Changes to the existing design:

There are currently no significant changes to the existing design. However, depending on the nature of the issue that causes Dr. Vichik’s design to fail, changes to our design might be necessary.

Changes to the project schedule:

Similarly, there are currently no significant changes to the project schedule. We might have to delay PCB layout and manufacturing if finding the solution takes more time than expected.

Answers to additional questions:

Part A:

It is difficult to say whether our product can meet a specific need with regards to global factors. While it can be said that the capability to solve optimization problems faster and more efficiently has a wide range of potential benefits, it is unclear which specific benefit our work will entail. Some potential global benefits include MPC for safer vehicle controls, which would benefit the transition to electric vehicles globally.

Part B:

It is difficult to say whether our product can meet a specific need with regards to cultural factors. This is mainly because our product only serves as a proof of concept for the possibility of solving optimization problems faster and more efficiently than existing solutions. It is hard to predict how our solution will be modified and integrated into other products, and thus we cannot say if our product will meet specific needs in relation to cultural factors.

Part C:

Our proposed product has the potential of yielding a positive environmental impact. Optimization is widely used in process engineering, which focuses on optimizing industrial and logistical processes. By improving the speed of solving optimization problems, many industries and logistical systems can be made much more efficiency in terms of energy consumption and resources usage. In addition, solving optimization problems on digital computers can be very energy-intensive, while our proposed analog solver consumes much less power. We also plan to use RoHS-compliant components, as well as lead-free PCBs, to reduce the amount of harmful substances in our product. Therefore, our product has the potential of contributing to sustainable development.

Part A was written by Andrew, Part B was written by Alvin, and Part C was written by Thomas.