Contingencies (Risk Management)

Due to the instability of the situation, we need to plan for the contingency that our necessary hardware cannot be shipped to us. We are already planning to calculate clock cycles necessary to perform essential hardware operations in simulation. We can calculate the model throughput of the entire system using numbers acquired in simulation:

We can calculate an estimate of the model throughput of the system using the following method:

|

`

Ta = Nm * (LB) + (LD) Tt1 = (C1) * (50M clock cycles per second) TN = N * Tt1 M1 = NM / (Ta + TN) MN = sum of M1 for each board in use |

Our simulated estimate for model throughput can then be compared to the model throughput of the CPU and GPU hardware setups, in case we are not able to build the system and measure an end-to-end metric.

The rest of our Team Status Update is below:

Accomplishments

Theodor fully defined a control FSM for the Convolutional Forward FPU operation, which also defines the upper limit of requirements for the FPU Job Manager (i.e. how many registers are needed, whether specific ALU operations are necessary).

Mark finished a framework for the Worker Finder, using a UDP broadcast as discussed and verifying the framework using a local server that emulates the Rasp Pi.

Schedule and Accomplishments for Next Week

Theodor will begin implementing the FPU Job Manager in SystemVerilog.

Mark will be working on the Workload Manager.

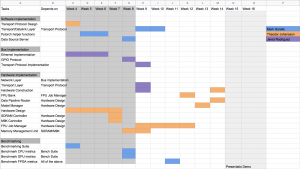

Updated Gantt Chart