This week, I transitioned from working on the communication portion of our project to working on the DUT. Namely, I finalized our ISA and designed the datapath for our DUT.

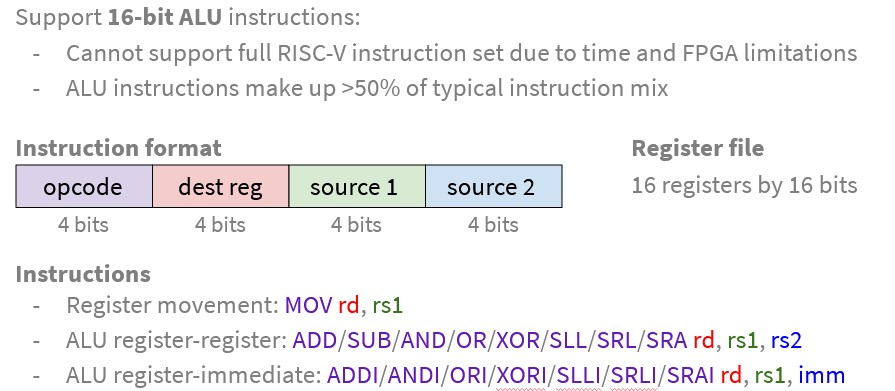

Designing the ISA involved several decisions: deciding 1) the number of bits, 2) the instruction format, and 3) the instructions themselves. For 1), I settled on 16 bits because it allows us to lesson the communication cost of the system, while still keeping the number large enough that it doesn’t become a toy example. For 2), I used the simplest scheme I could think of in the interest of making our instruction decoder simple, as is typical in a RISC architecture. For 3), I examined ISAs I have studied (x86, ARM, RISC-V) and chose 16 arithmetic/logical instructions that are in most ISAs, as these are the crucial ones.

I also designed the datapath for our DUT: a single-cycle microarchitecture implementing this ISA. There aren’t many design decisions involved here. I simply chose the most simple datapath with my computer architecture knowledge.

In addition to these individual tasks, I also worked on benchmarking simulation speed and the design review slides.

It should be noted that my action items did change this week from what I had planned. I originally planned to start working on the golden model this week, but given that it would be nice to have a concrete diagram of the DUT for the design review, I prefeteched the task of designing the datapath. However, I am still on track to meeting my deliverables. Next week, I will work on and finish the golden model.