- Risks

- This week we fixed several risks, including low laser power and the FTDI power chip not working. However, we also added several more:

- One is that Macs do not support our usb power plan. We need to find a new power solution. We plan on researching available usb splitters and powered usb hubs that may fit our needs. Worst case, we can either hand splice a wire to separate power and data or we can use a power supply separate from USB. However, we plan on looking into better alternatives than that.

- Another risk is that the comparators do not work. Our original comparators for our receivers do not work as well as the datasheet suggests, and therefore our circuit does not create enough overdrive voltage for them to have digital outputs. To mitigate this, we purchased 2 different new comparator chip models that should perform better. They are the same footprint and will work perfectly if the datasheets are correct. If they both end up not working, we can wire in a breadboard with more analog circuits to fix this. However, that would greatly limit our max communication speed, so we are trying new comparators first.

- Simulation on the FPGA had difficulties running due to subtle syntax differences. The biggest of these were debugged, but the ability to easily verify it might be time-consuming in the future.

- Design Changes

- We will need some new part to fix our usb power delivery issue. This is not yet determined, but will likely be something between our board and the laptop.

- We changed how we will be 3d printing the lens housing. Rather than 3d printing threads or a hole for self tapping, we will cut the metal housing we have down to a small size since it has threads that fit our lens already. Then, we just need to 3d print a circular hole for the housing to sit in, which requires much less precise work.

- We plan on removing the sequence tag ID, once we verify that all of the packets can be performed in-time synchronously. This will be dependent on the speed that the computer can read data off the FTDI, verify the Hamming code, and send data back.

- Updated Schedule

- The actual 3d print and assembly of our lens housing has been pushed to next week due to issues with the board that came up this week.

- Board testing continues to be extended as we encounter unexpected issues with the boards.

- FPGA testing will continue on next week, waiting for software and hardware to work before integration.

- Progress

- The board powered over 9V USB PD by configuring the EEPROM connected to the FTDI chip:

- Currently debugging, but a full FSM and datapath for the FPGA was designed and programmed.

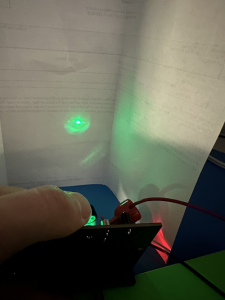

- Higher power laser output was produced that can be read better by receivers.

- The board powered over 9V USB PD by configuring the EEPROM connected to the FTDI chip:

KJ Newman’s Status Report for 3/25/2023

- Work this week

- This week I debugged several issues with our PCB. One of these is that the receivers do not work. This is because our comparators are not behaving as specced. They are specified as low as 20 mV overdrive with no minimum spec, but we experimentally found that they only work starting at 50 mV overdrive. Our TIAs do not create a large enough voltage swing for this, so they do not output digital values. To fix this, I ordered 2 new comparators that have several specs well below this, as low as 5 mV overdrive. They still do not have a minimum spec but appear to be better. I also made sure to get chips from different manufacturers in case this is a manufacturer issue. These will arrive next week for testing.

- Another board issue detected this week was laser power. The lasers have visibly inconsistent power output, mostly weaker than expected. I did some experiments and determined that this is because the threshold voltage of our laser diodes is not consistent. To fix this, I connected lasers to external power and used experimental and datasheet values combined to calculate the feedback current that equals our expected optical powers, 2.5 mW and 0.5 mW. I then tested how much input current would create that feedback current for individual lasers. I did this for both lasers on one board and replaced the resistors to equal this power, which makes the board now have the correct power. I now know each laser needs this calibration individually, so will need to do it on the other board too.

- Another issue detected this week was power related. I managed to program the FTDI chip on one board to the correct communication and power settings, but I discovered that the board only successfully draws 9V from a laptop charger, not from my laptop. This is despite Apple customer support explicitly stating that this would work. It seems Macs do not support being a USB PD source above 5V. To fix this, we will need to splice wires or find some device capable of high voltage USB PD and data combined.

- I also received new USB connectors this week, and attached one to our second board. This was much faster and easier than the first, since I had to figure out a method the first time. This time, it worked on the first try with no damage to anything.

- I tested various methods to see what the best way to test a single board is, since we need both a transmitter and receiver to test anything. The best method I found was using a small reflective piece of metal to reflect the unfocused laser back towards the receiver on the same board. This is strong enough to trigger the photodiode and TIA, so this is how I have been testing the receiver.

- Schedule

- Due to the specified board issues, I did not 3d print our lens housing this week. This will be pushed once again to next week. I have made a plan for exactly what shape needs to be made, but do not have CAD for it yet.

- Deliverables

- Next week, I plan to deliver at least one housing for the lens. However, the important deliverables are fixing the circuits. I plan to have fixed the laser power on the second board and have fixed the receivers to properly output digital signals using one of the new comparators. Additionally, I want to have settled on a solution for the USB power, even if it is not implemented yet.

Anju Ito’s Status Report for 3/18/2023

- Work This Week

- Began to write FPGA code. Progress:

- Wrote a laser transmitter module that will transmit 2 input data over 2 lasers if the data valid signal is set. This module will always transmit both data simultaneously. This is the desired behavior for the project, as our MVP will never use one laser and not the other.

- Wrote a laser receiver module that always listens for a byte that follows UART protocol (start bit and stop bit). This module was configured so it can only receive both at the same time, and currently making different versions to test the receiver.

- Debugged the laser transmitter and receiver by setting up the waveform viewer environment. This took some time, as the vcs compiler kept exiting on failure. It turns out that the source bashrc has to be called every time, and I have to make sure that I only have setup447 (or one of the class) and not the other, as those conflict with each other now.

- Wrote an untested version of the FSM and protocol handler of the transmitter module.

- Verified functionality of the transmitter and receiver modules by sending constant bytes from the transmitter to receiver using a single board, connected by jumper cables from the laser out line to the laser in line. Successfully sent bit, flashing the data received every time, and allowing for switches.

- Imported pin configurations and assigned appropriate ones based on schematic. Modified code so that all GPIO pins except for transmitting and outputs are high impedance, and labeled/used each one for its set purpose.

- Flashed the code successfully onto FPGA non-volatile memory. This involved emailing/creating a Terasic account to get their programmer, and converting file formats. This makes it much easier to just turn on the device without needing to reconfigure the board every time.

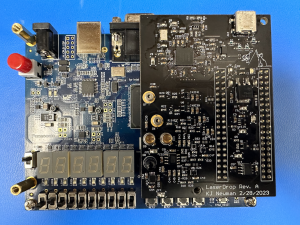

- Integrated the FPGA with the PCB. Fixed issues with DNP resistor labelling that caused the FPGA to be turned partially on (3V3 was connected instead of the 5V to the FPGA. Fixed by removing and putting on the resistors). Verified that the lasers can be somewhat controlled by the FPGA, although there is no way to test it so far as the receiver did not work with preliminary testing using mirrors.

- Began to write FPGA code. Progress:

- Schedule

- Things are on schedule. Since boards have arrived and KJ has assembled them, my implementation from now will most on likely work in parallel with testing the board features and making sure that they will work. This will involve modifying the code and making a simplified version of it which would take some time, but also ensure that the code will work well with the board.

- In addition, since there are potential issues with the receiver and we need to verify the functionality of the lasers, etc. I will use some time attempting to write test code and debugging that feature, which may slow down me working on FSM.

- Next Week

- Write out the full program for FPGA including the receiver FSM, and testing the transmitter FSM. Integrate it with the board and see how far I get.

- Test out the laser transmitter/receiver on the PCB, because integrating with the FPGA may be the easiest way to test the board functionality, since it receives high speed transmission. Since it didn’t register the first time transmitting at 6.25 MHz using a mirror, potential things to do are slowing down this transmission speed greatly, using 2 boards for better laser power going to the other board, turning off ambient noise cancellation, and testing in a dark room.

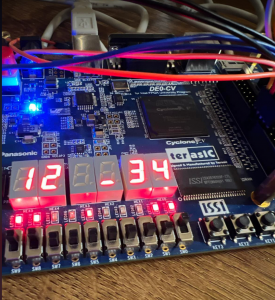

Bits being transmitted and received by the receiver module (displayed on the HEX values, the first 2 for the IR receivers and the second 2 for the green receivers). The GPIO pins are connected with jumper cables.

Team Status Report for 3/18/2023

- Risks

- The IR receiver on one board appears to be floating. This is not a huge risk because it is likely a poorly soldered part, but there is a risk that there is something big wrong. We will be looking into this next week to determine exactly what is wrong.

- We tried to do a quick test of the receiver, which did not work. This is most likely due to poor setup, but it may require figuring out how the ambient light filtering works, and how best to aim the boards to each other in order to test accurately, which may take some time and work.

- Design Changes

- Our USB connector did not fit properly on our board, so we needed to bend pins and not attach all pins in order to get it connected. This ultimately resulted in some power and ground pins not being connected as planned. This is not expected to cause any issues but does mean that our board supports less current going through the connector now.

- When writing the FPGA program, we’re slightly split on whether to make it so that both lasers must receive at the same time and transmit at the same time. If we do this, it would add integrity because there is a much smaller likelihood that both would turn on accidentally at the same time, and make handling the protocol easier. However, it would also make it so that testing is difficult. Right now, the decision is that it will only handle simultaneous receiving/transmission, and the code will be modified slightly so that testing can be done with just one.

- Updated Schedule

- We did not do any 3d printing this week due to the assembly process taking longer than expected. This will now happen next week.

- The implementation of the FPGA got slightly overlapped with board integration, and some of the code development would be shifted to testing using the actual PCB.

- Progress

- Boards complete!

- FPGA code written and tested for the laser and receiver module. The FSM that handles the actual protocol behavior is written on the receiver side, but not yet tested.

- FPGA and board integrated, and ensured that GPIO pins control the appropriate circuitry.

- Boards complete!

KJ Newman’s Status Report for 3/18/2023

- Work this week

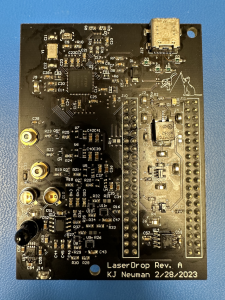

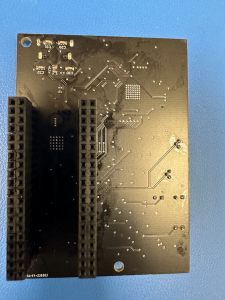

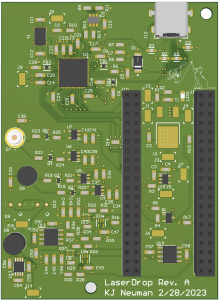

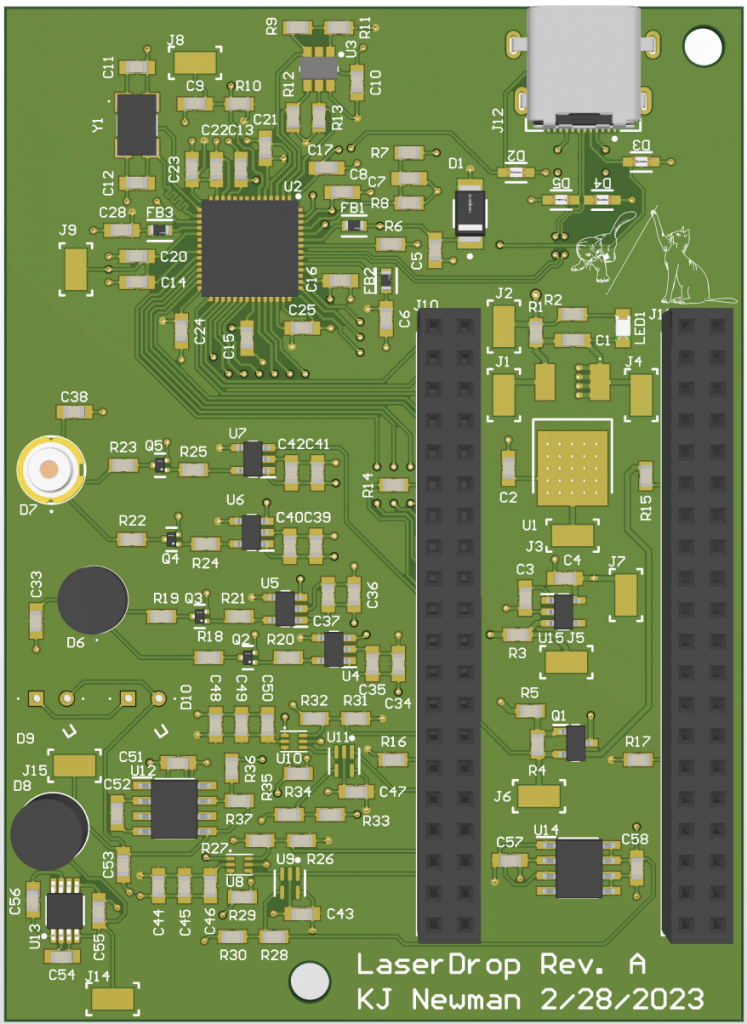

- This week, I assembled two of our PCBs. We did not receive a stencil from JLCPCB, so this took quite a while. The boards assembled as expected with only one exception, the USB connector. The connector requires a board cutout underneath it and the board does not have one, so it took a lot of time to get the connector to fit. Ultimately, I figured out a way to bend the pins and use hot air soldering to get the connector on, but destroyed our 2 other connectors in the process. However, it did work on one board, so we ordered some more connectors to put on the second PCB using the same process. This ultimately will not slow us down much or cost much. The board is shown here:

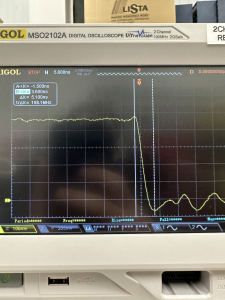

- I also tested the PCBs. The transmission and power circuits work as expected, and the receiver circuits are difficult to test without FPGA software, so I began working with Anju on integrating the FPGA board and the custom board. Transmitting works integrated with the FPGA, and receiving testing is ongoing. All voltages on the board are correct, and laser driving at two different power levels works with sufficient rise and fall time to transmit at our speeds as shown:

- I verified how the lenses fit over our board and that they properly focus both lasers. I also found that iPhone cameras can indeed see our IR laser, but not very well

- I ordered some additional parts this week. I ordered and received 3d printer filament. I also ordered new usb connectors as we ran out.

- This week, I assembled two of our PCBs. We did not receive a stencil from JLCPCB, so this took quite a while. The boards assembled as expected with only one exception, the USB connector. The connector requires a board cutout underneath it and the board does not have one, so it took a lot of time to get the connector to fit. Ultimately, I figured out a way to bend the pins and use hot air soldering to get the connector on, but destroyed our 2 other connectors in the process. However, it did work on one board, so we ordered some more connectors to put on the second PCB using the same process. This ultimately will not slow us down much or cost much. The board is shown here:

- Schedule

- My work is mostly on schedule. I managed to assemble and test pcbs despite not having the stencil. However, this meant that 3d printing our housing fell behind schedule, and I now plan on doing this next week.

- Deliverables

- For next week, I plan to design our 3d printed housing for the lenses and print it. I also plan on continuing integration of the receiver with Anju and giving a board to Roger for him to integrate USB code and EEPROM settings onto.

Roger Lacson’s Status Report for 3/18/2023

- Personal Accomplishments

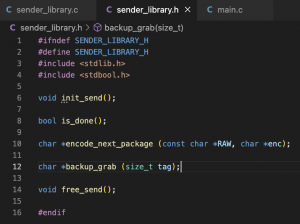

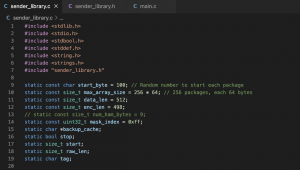

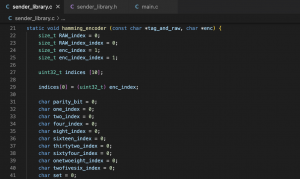

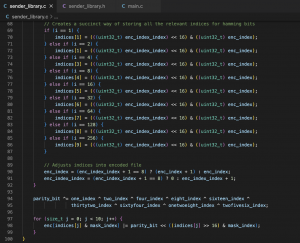

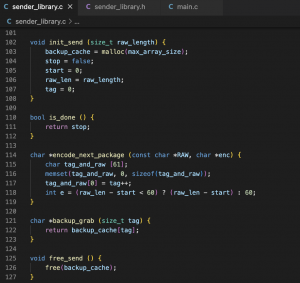

- I have finished implementing background software for processes not involving hardware, consisting of sender and receiver libraries for processing information.

- Anju and I collaborated on updates that should simplify the protocol. Before, we were going to concurrently send packets, decode on the receiver side, have the receiver signal for resending packets upon hamming error (which would involve a receiver side error queue and a sender side cache), and final reconstruction revolving around tags (involving a priority queue on the receiver side). We have since simplified this procedure. We will now only send packets one at a time until it passes both UART checks and hamming encoding checks in software. This will save us the trouble of trying to interrupt flow processes based on errors that might occur, and guarantees that on the receiver side, all information received and stored will be correct (based on the limitations of hamming encoding) and present. This also removes complications such as caching packets in the case of error on the sender side, and the priority queue on the receiver side. Additionally, the entire file size will be sent up front so appropriately sized memory can be allocated upfront on the receiver side. This has significantly decluttered and streamlined my code and should hopefully minimally compromise on time, if at all.

- I completed steps 1 and 2 for the Ethics Assignment

- Schedule

- My schedule is mostly on track now. I would like to write more test cases to double-check that my code is functioning properly. I can now proceed to work with KJ on programming an EEPROM and VCP with the hardware being completed this week.

- Deliverables for Next Week

- More test cases for current code

- Code that demonstrates a basic understanding of interfacing with the hardware (EEPROM and VCP code)

- Begin fully implementing software that integrates the library code I have written into sender and receiver code for the device.

Roger Lacson’s Status Report for 3/11/2023

- Personal Accomplishments

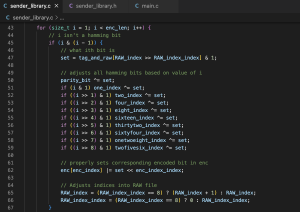

- I have begun implementing the software to process files and bitwise hamming encode them. The progress I have made on my code is screenshotted below.

- I have decided to use a somewhat less space-efficient method for caching old packages (in case errors occur and packages need to be resent) in favor of speed and ease of understanding.

- I wrote my part of the design report. Doing this in parallel with implementation hindered my implementation progress, but I hope to have sender and receiver library code finished by the end of the week following break.

- Schedule

- My schedule has been adjusted. We were hoping to have hardware fully finalized before break so I could begin implementing software to implement with our devices, but we only finalized the device right before the break. As such, I moved onto other coding challenges to maintain the timeline, namely, the implementation for the software processing of packets from the sender side, as well as writing pseudocode and adjusting it for the receiver side.

- Deliverables for Next Week

- I plan to have full implementations for the sender and receiver codes, separate from the hardware interfacing itself. This should prepare me to tackle challenges related to hardware in the following week, namely, VCP implementation and EEPROM programming, both of which, I do not have experience with and will need time.

- Well-documented and thorough testing of my implementations and helper functions

Anju Ito’s Status Report for 3/11/2023

- Work This Week

- Significant amount of time was spent working on the design report this week, including FPGA implementations, diagrams, and overall project information.

- Began coding modules for clock dividers that will be needed to time UART communication on the USB transceiver and laser side.

- Came up with block diagram for the transceiver, consisting of 2 shift registers that will be enabled depending on number of bits that go into each.

- Schedule

- Design report took more amount of time than originally thought. Implementation will need to be worked on, which will hopefully be done the week after spring break.

- Next Week

- Have an overall implementation of all aspects of the FPGA, so that debugging can be conducted the week after using oscilloscopes for signal accuracy

Team Status Report for 3/11/2023

- Risks

- With the complete PCB design, we removed some of the planned backup plans since they were not feasible. The big one is that we were planning on leaving some extra DNP pads for more green photodiodes in case our photodiodes are not strong enough. However, there is slightly more risk now since we had to remove this to make layout work.

- We noticed that the FPGA board lists some pins as clock pins. The Datasheet does not describe what this means. This is 2 pins from the FTDI chip and the 2 IR laser controlling pins. If this ends up being an issue, we can accommodate it by using an interface with the FTDI chip that does not use those pins (fast serial) and by testing that the IR laser pins operate at high enough speed.

- Design Changes

- Our PCB will be much smaller than the FPGA board rather than a copy of it. This is because the parts fit on a much smaller footprint, and making it smaller makes buttons and LEDs on the FPGA board accessible, and it will be easier to make sure the boards fit together.

- Updated Schedule

- In terms of schedule, software developments (Roger) were impacted by inability to develop software for hardware that had not been fully finalized. We have instead begun working on sender implementation as well as a preliminary UI interface to input text files for sending in order to be productive within the schedule constraints.

- No changes have been made to the hardware schedule as the PCB and part orders went out on time

- Progress

- PCB design is complete! Our PCB and all components for it have been ordered and should arrive by the time we return from spring break.

- Sender implementation for the bitwise hamming encoding of files has been implemented

- We completed our design report paper

- PCB design is complete! Our PCB and all components for it have been ordered and should arrive by the time we return from spring break.

- New Tools

- We will need to learn to use FT_PROG to program the EEPROM to save settings for our FTDI chip

- We will need to experimentally identify the best way to view the infrared laser for debugging and testing. We currently plan on using the front-facing camera from our phones, as they typically do not have IR-cut filters. However, this may not work. In that case, we will need to learn to use an IR camera to measure it.

KJ Newman’s Status Report for 3/11/2023

- Work this week

- This week, I completed our PCB design. I did our layout and it passed all DFM checks. It is currently in fabrication at JLCPCB and expected to arrive before class resumes after winter break.

- I ordered all parts to make our PCB. Our only expected expense that has not been purchased yet is 3d printer filament. This has 1 day shipping so can be purchased later. Setting up our part orders was a bit complex because I wanted to order with bulk discounts where possible and buy extra components in case we need them, but we are running a little close to the $600 budget. I ultimately ordered enough active components for 3 boards and numbers of resistors and capacitors to get bulk discounts.

- I wrote my parts of the design report. This was a lot of work to do in parallel with finishing and ordering the PCB, but we managed to finish it.

- This week, I completed our PCB design. I did our layout and it passed all DFM checks. It is currently in fabrication at JLCPCB and expected to arrive before class resumes after winter break.

- Schedule

- My parts are on schedule. I planned on having the pcb ordered before spring break and set to arrive after spring break, and it should be here by then.

- Deliverables

- For next week, I plan to have 2 PCBs fully assembled and ready for use. This should be achievable, since all of our parts will have arrived before the beginning of the week.