- Work this week

- Finalize laser transmitter/receiver and FTDI interface

- All inputs go through 2 flip flops to avoid metastability

- Better timing for all I/O devices

- Implement handshaking

- Handshaking occurs before every packet send now

- Series of 0xAA sent by transmitter. Receiver responds with 0x10

- Implement packet sending/receiving

- Sender: send bytes in 1kB chunks. Handshakes before each one.

- Receiver: receives bytes. If receive < 128kB after handshaking, will pad out the bits with all 1’s

- Use 128kB buffer on receiver/transmitter

- If more than 1kB sent/received, FPGA has capability to store that.

- Created to accommodate for slow USB transmission.

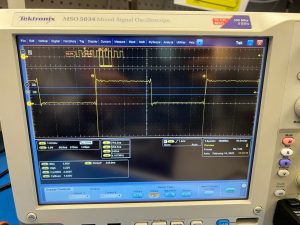

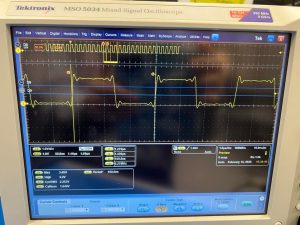

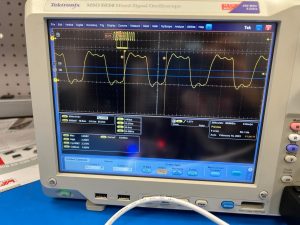

- Create Manchester/Duty-cycle like encoding for FPGA

- Made the last half of each bit a 0. We found out during testing that the ambient light filtering would adjust to the laser light level if we were transmitting a lot of 1’s in a row. In order to mitigate this, we made half of each bit a 0, and sample on the first half.

- FPGA Cycle Counter

- Added debugging counters to report how many clock cycles packets stay on the FPGA.

- Measured from the point that the transmitter FPGA saw data on the FTDI chip until the receiver FPGA received and put the data onto FTDI chip.

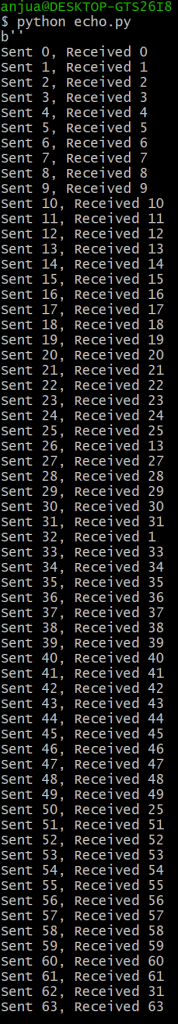

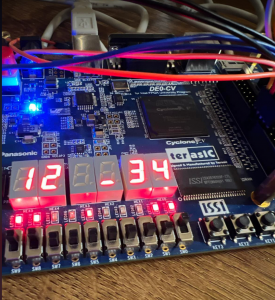

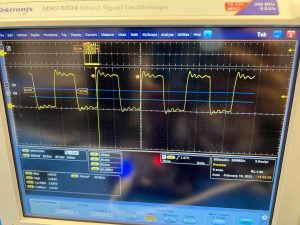

- Debugged a lot of FPGA code using setup where FTDI code was connected to the FPGA, and laser receiver/transmitter connected via jumpers to each other.

- Finalize laser transmitter/receiver and FTDI interface

- Schedule

- We are cutting into slack, but the core part of the project is done. We have moved onto integration and testing. In terms of work, this has transformed into adding/getting rid of debugging features for testing and design trade-offs. We have successfully transmitted a large file (19MB) over lasers, and reached MVP!

- Next Week

- Continue working on integration. See the best methods of transitions and talk about design decisions at full-scale level. Refine.

- Work on design report/poster/presentation.

FPGA setup used for debugging