- Work this week

- Integrated RAM use on the FPGA. Created a 1k FIFO using Quartus IP, and successfully integrated into the code. This fixed the error of not having enough logic components to compile the design on the FPGA, and instead using the embedded RAM on the chip.

- Fixed a FSM logic bug that prevented the FPGA from transmitting 2 bytes in a row over the lasers.

- Fixed timing issue for writes onto the FTDI chip. When testing with lasers, occasionally saw that the 6th bit in the byte was always a one. There was a logic error in the setup time that resulted in data not being held for an appropriate length before the write was asserted.

- Finished writing code and loading all the files for demo. Created a board that can be configured to echo just using the FTDI chip and back, and another that transmits whatever it receives through the USB on the laser and writes back whatever it sees on the receiver back to the USB. Also attempted to test by turning the lasers completely off and on, board-to-board transmission (worked much more poorly then single board using mirrors), and turning ambient light filtering off (not work too well).

- Attempting to fix the board-to-board by creating mounts for the PCB so that they are more stable.

- Working through making the receiver more robust. Cleaned out logic, which may have made it slightly better. However, still occasionally see duplicates in numbers during laser transmission, which needs to be fixed/explained.

- Schedule

- Everything that we prepared for the demo we were able to show, although there are new issues such as the necessity of extremely precise alignments and receivers having errors that need to be addressed in the future. Everything is around 2 weeks behind schedule, as implementation is taking a longer time than planned.

- Next Week

- Attempt to make laser transmission code more robust. Currently seeing duplicates and wrong bits too regularly.

- Potential solutions: Fix any bugs that exist, slow down transmission speed from 6.25MHz, change how the receiver is sampling, add real-life flaws onto simulation to attempt to get error, 3D printed mounts

- Implement handshaking protocol.

- Work with integration and start testing.

- Attempt to make laser transmission code more robust. Currently seeing duplicates and wrong bits too regularly.

- Testing/Verification

- Unit Tests

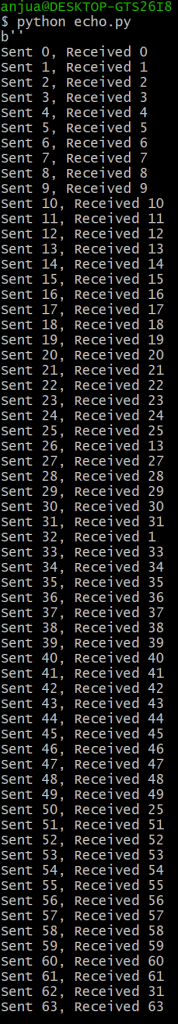

- Echo to test FPGA/FTDI/computer connection: Test that verifies the connection between FPGA to computer by computer writing/reading bytes, and the FPGA echoing that back through the FTDI.

- Verified. Attempted to time, and realized that computer’s read function especially takes a long time to run, but the number of bytes read doesn’t affect speed.

- Laser transmission test: Verifies that the whole pipeline from computer to FPGA to lasers work with single byte.

- Verified. However, alignment changes results a lot, and multiple bytes become less stable.

- Packet send test: NOT DONE. Send a full packet, and verify that it was received correctly on the other side. Should not load it onto the FPGA if the start sequence is not received properly.

- Echo to test FPGA/FTDI/computer connection: Test that verifies the connection between FPGA to computer by computer writing/reading bytes, and the FPGA echoing that back through the FTDI.

- FPGA Integration Tests

- Stress Test: fill FTDI chip multiple times, see if it can process data appropriately

- Speed Test: measure pin out speed with oscilloscope to verify laser transmission

- Light Test: Try testing in different lighting environment to see that transmission works under reasonable room conditions

- Distance Test: slowly move the boards away from each other. Adjust focus, and record the max distance bytes can be transmitted at.

- Unit Tests

Anju Ito, Roger Lacson, and KJ Newman