What are the most significant risks that could jeopardize the success of the project? How are these risks being managed? What contingency plans are ready?

What are the most significant risks that could jeopardize the success of the project? How are these risks being managed? What contingency plans are ready?

PCB Development:

Based on discussions with the Professor & TA after receiving our Design Review feedback, we realised there may be more challenges surrounding custom PCB development than we had previously planned for. We had originally planned on using the STMWB Nucleo board we are currently using for testing and development as a point of reference for our PCB design, however we have realised this is not sufficient to ensure seamless integration with our selected peripherals. To address this we have completed additional research on the specs of our STMWB processor and are currently prioritising drafting & manufacturing an initial design so we can start testing.

BLE Connectivity:

Whilst working on initial development & testing STMWB Nucleo board , we have discovered that the integrated BLE module is not always reliable / is more challenging to work with than we initially thought. To address this issue we are looking more in-depthly at documentation & integrating external crystals. As a last resort back-up option we have also looked at replacing our microcontroller with an Adafruit feather.

Were any changes made to the existing design of the system (requirements, block diagram, system spec, etc)? Why was this change necessary, what costs does the change incur, and how will these costs be mitigated going forward?

At this point in time we have not made any overall changes to the structure of our system, however as previously mentioned we have had to work on updating the schematics proposed in our design review .

Provide an updated schedule if changes have occurred.

As mentioned above, we have slightly moved around our proposed schedule to ensure we have ample time to refine our PCB design. Our goal is to have a draft of our design as soon as possible to account for time and cost expenditures if several rounds of prototyping are required.

Additionally, during early March all of our group members were preoccupied with external commitments (phD visits, conference, other project due dates etc.) so we did not have much time to progress on our capstone work. Whilst we did initially plan for these shortcomings, we are still slightly more behind than projected and have had to adjust our workload to accomodate this.

Please enumerate how you have adjusted your team work assignments to fill in gaps related to either new design challenges or team shortfalls.

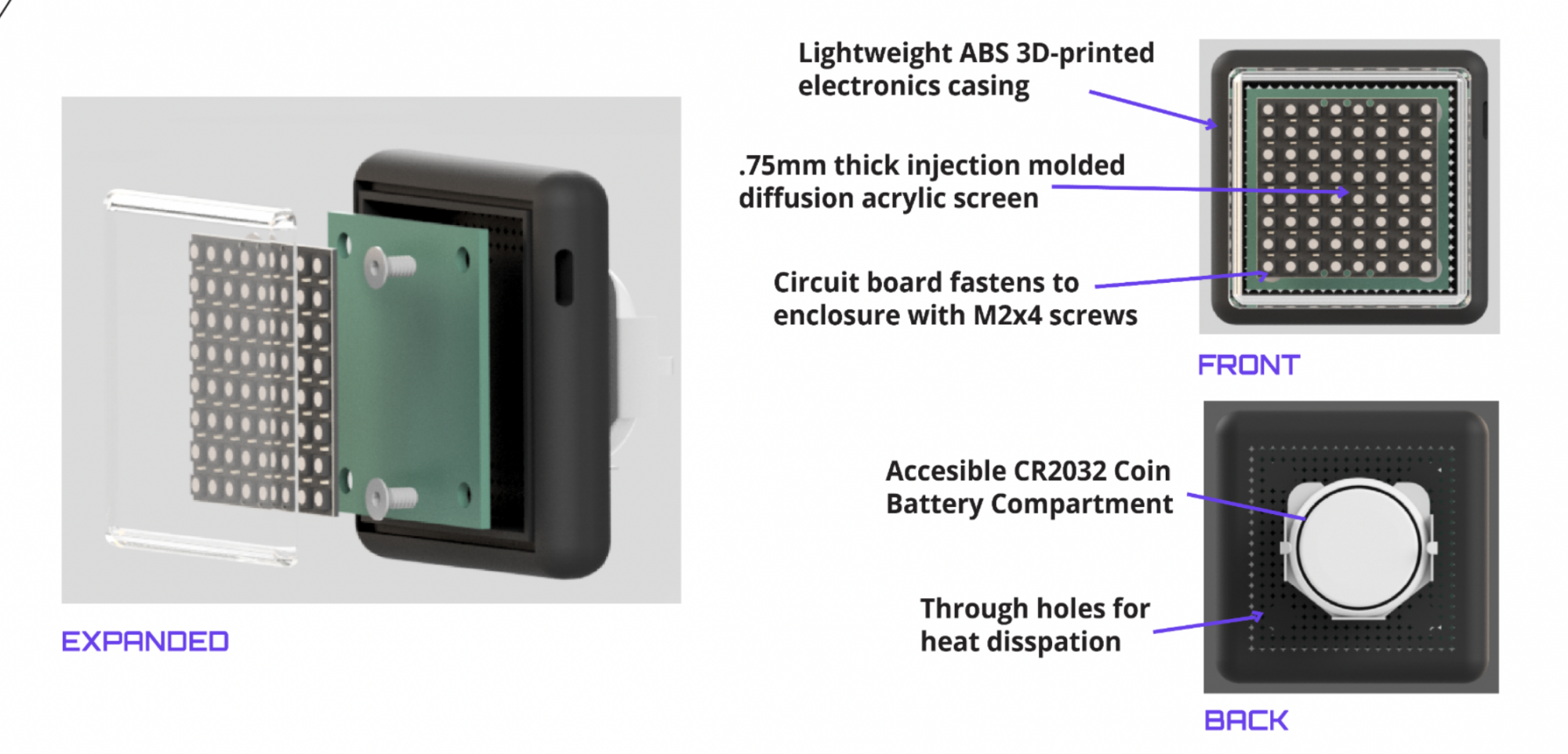

Saniya has swapped from working in between the software / hardware tasks, to primarily focus on PCB design to assist Shize. As a key part of our project is effectively miniaturising our system whilst balancing other design constraints, our group believes it is vital to direct our time/resources to this aspect of the project.