Jae’s Status Report 4/30

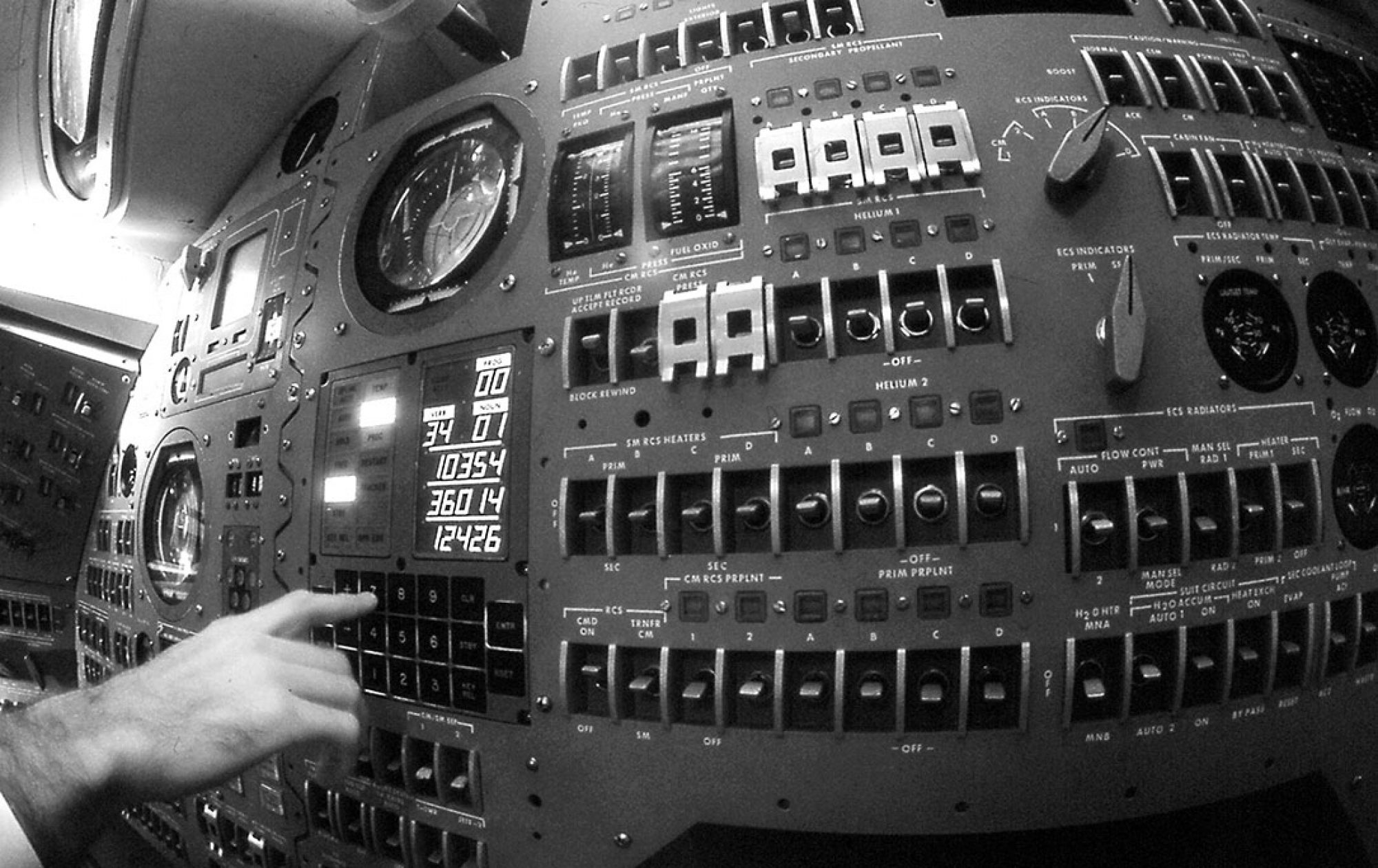

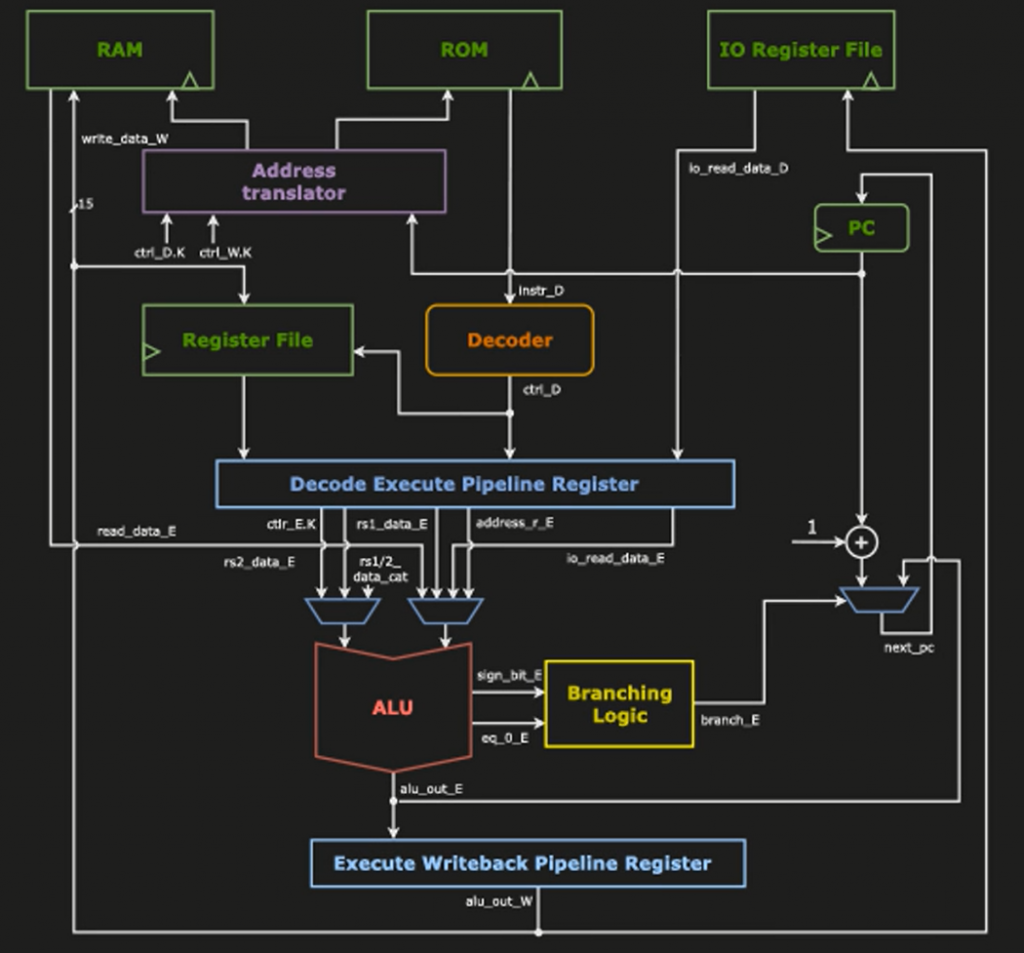

This week I spent most of my time catching a couple bugs in the implementation but mostly working on the video. I have decided that having some professional looking animations would help the audience comprehend some architecture level details (such as banked memory and the CPU pipeline) so I spent most of my time developing animations in After Effects. Below is a draft quality video of the CPU pipeline I animated. We are around 50% done with the video and I plan on getting more demo footage of the DSKY and completing the video by Monday/Tuesday. Wednesday and Thursday (after the Techspark Exposition) will be used for final preflight/pre-demo checks and some more bug hunting. We are very glad to have finished everything according to our plan and can focus on the video and the demo setup.

Jae’s Status Report 4/23

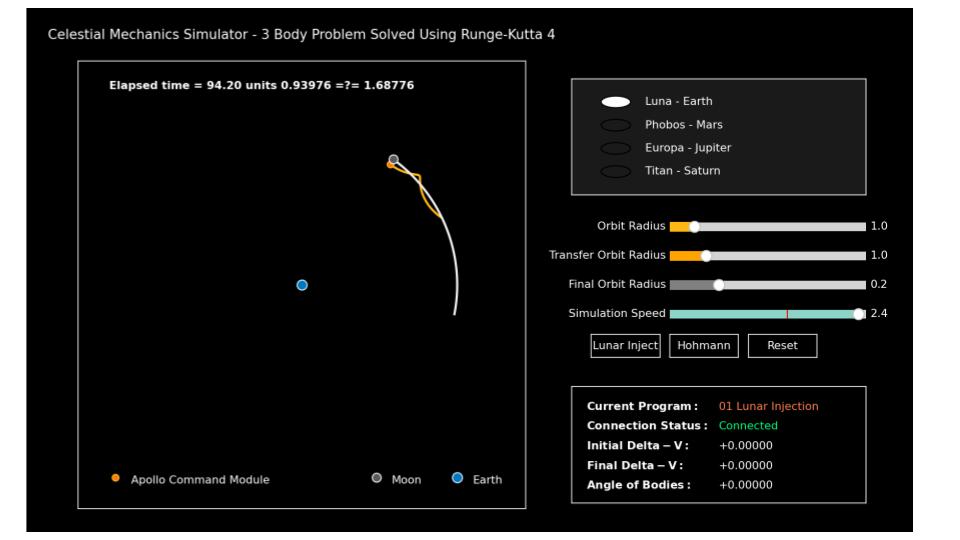

This was a very busy week of integration of the DSKY with the AGC and then with the demo software. Earlier this week, there were some obstacles getting RX and TX to work, but after their implementation the FPGA AGC was now running reliably. I was responsible for adjusting the DSKY firmware for integration with the AGC, which resulted in lots of unforeseen bugs, race conditions, and priority inversions with the ESP32 FreeRTOS. After majority of the bugs were fixed, I had to write our custom 3-body simulator (Runge-Kutta 4th order ordinary differential equation solver) and the interface to the ESP32 via wireless connection. Although some bugs remain, fortunately it is functional and therefore we have reached critical mass for our MVP demo.

My goal next week is to work on the video and further tune out the bugs in the ESP32 and the Python demo.

Jae’s Status Report 4/16

This week I completed the entire firmware for the DSKY, including the VERB-NOUN pair acquisition and the creation of packets to be sent through UART to the FPGA. Furthermore, I completed a Bluetooth module that will emulate as a “telemetry” between the AGC and Ground Station “Houston” or the Python demo script. The firmware is multithreaded (FreeRTOS) and therefore I ran into extremely unpleasant bugs with race conditions and priority inversions, but all issues have been finally resolved. The plan is to use the DSKY’s ESP32 module to receive mission data via Bluetooth, and allow the AGC to perform calculations on the data then send them back through the Bluetooth channels. At this moment, the DSKY firmware and hardware is fully verified and I plan on working on integration with the AGC and completing the Python demo next week.

Jae’s Status Report 4/9

This week I worked on finishing the entirety of the AGC Assembler code for the AGC. This mostly consisted of a simple FSM-like loop that selects appropriate program to execute when a correct program number is entered. For instance, VERB 39 NOUN 1 will run a program to calculate the delta-v required to escape a planetary body’s gravitational field (escape velocity). Other programs include calculating translunar injection velocities, Hohmann transfer orbital transfers, and orbital plane transfers. Furthermore, we realized that the SQRT function from the Apollo missions used instructions which were descoped, therefore I had to implement a custom single precision square root subroutine. The sine functions from the Apollo missions are still being used for calculations.

My goal for next week is to finish validating the AGC program and debug on our SystemVerilog implementation. I also plan on working on finishing the Python demo visualizer.

Jae’s Status Report 4/2

This week was spent mostly spent continuing to work on the demo programs for the AGC and studying more on the AXI-AGC interaction. For the demo, a simple visualization script running on Python will demonstrate the orbital mechanics calculations of the AGC. To do so, AXI will be used to send simulation mission data to the AGC, and after the AGC calculates required orbital delta-v or other parameters, will send the calculation results back to the AXI to the python script. I will be running a simple 3-body simulation of the Moon, Earth, and the space-craft. For the visualization library, I will most likely use matplotlib to plot a simple 3d motions of the planetary bodies and the spacecraft.

I will continue to work on finishing the DSKY firmware next week, especially since I am now aware of the I/O specifications from the AGC Verilog code. I will then finish up the AGC demo code.

Jae’s Status Report 3/26

This week I was responsible for working with Don to make sure the microcontroller on the DSKY and the I/O driver that Don was building spoke with common protocol. Since we were using UART, we decided to go for a plaintext communication such that we can easily debug using a serial terminal window. We gained insight into how to send display data packets to the DSKY and how the DSKY was going to send NOUN/VERB numbers to the AGC core.

I was also responsible for bringing up and verifying that the math functions (SIN, COS, SQRT) were operational and accurate. These functions were from the original Apollo missions so therefore they were well implemented, We are now ready to start writing code for the demo and test on the architecture once it is up and running.

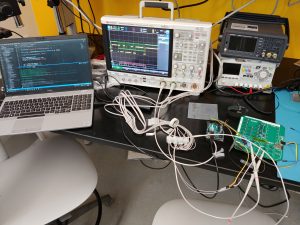

Jae’s Status Report 3/19

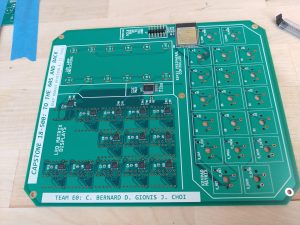

This week and the previous week I primarily worked on finishing the board. At this point in time, the board is fully functional and no design issues were detected. The board bring up was actually not painless at all however, since all the useful gear at Techspark were not operable due to the lack of staff during the break, therefore everything had to be hand placed and hand stenciled. Furthermore, the stencil received was thicker than ordered, therefore this resulted in many solder bridges that I had to manually fix with a soldering iron under the microscope. Afterwards, an acrylic was laser cut and keycaps and standoffs were installed, completing the piece.

My goal for next week is continue working on the ESP32 software (https://github.com/Absolute0K/DSKY-firmware) and researching the AXI interface for the FPGA-ARM communication for the demo.

Jae’s Status Report 2/26

This week I was responsible for watching and filling out the peer reviews for my section, as well as rehearsing and delivering my presentation on Wednesday. Meanwhile, I completed the first revision of the PCB and resolved all the ERC (Electrical Rule Check) for my schematics and DRC (Design Rule Check) for my PCB. I quadruple checked my schematics against all the component datasheets and made sure my design rules were all within specs for PCBWay (our PCB fab). I am currently on track to do another round of final checks and begin the process of sending out the gerber files. In the upcoming week, I will start the purchasing process of the PCB as well as the components from Digikey. With the components/PCB purchased and on route, I will begin the firmware/software development process as I wait.

Jae’s Status Report 02/19

This week my primary focus on the programs that will be run on the AGC and finishing up the first revision of the PCB. I have been analyzing sample AGC assembly routines and experimenting with certain basic instructions (such as XCHG, MUL, DV, etc.) to get a feel for how to develop code for our implementation. I have also identified certain subroutines used by the actual Apollo missions that we will be able to run on our architecture with minimal to no changes. This will be a nice demonstration of the correctness of our implementation. Finally, I have more or less finalized the first revision of the board. Next week, I will triple check my schematics and layout and get ready to send the gerber files out to be fabricated. Also, I will continue experimenting with the AGC Assembly language to build some proof-of-concept programs.