Donovan’s Status Report 4/30

At the very beginning of the week, I spent most of my time preparing to deliver the final presentation. Once that was complete, my focus shifted to video production tasks. Christopher and I wrote multiple revisions of a script for our video’s intro and ISA description. I’ve continually provided Jae necessary information to develop video animations that accurately convey the points we are making about the architecture. Lastly, I recorded my speaking part for the video intro and transition into the architecture discussion. I will continue work on video production and begin preparing the final report as we enter the final week.

Jae’s Status Report 4/30

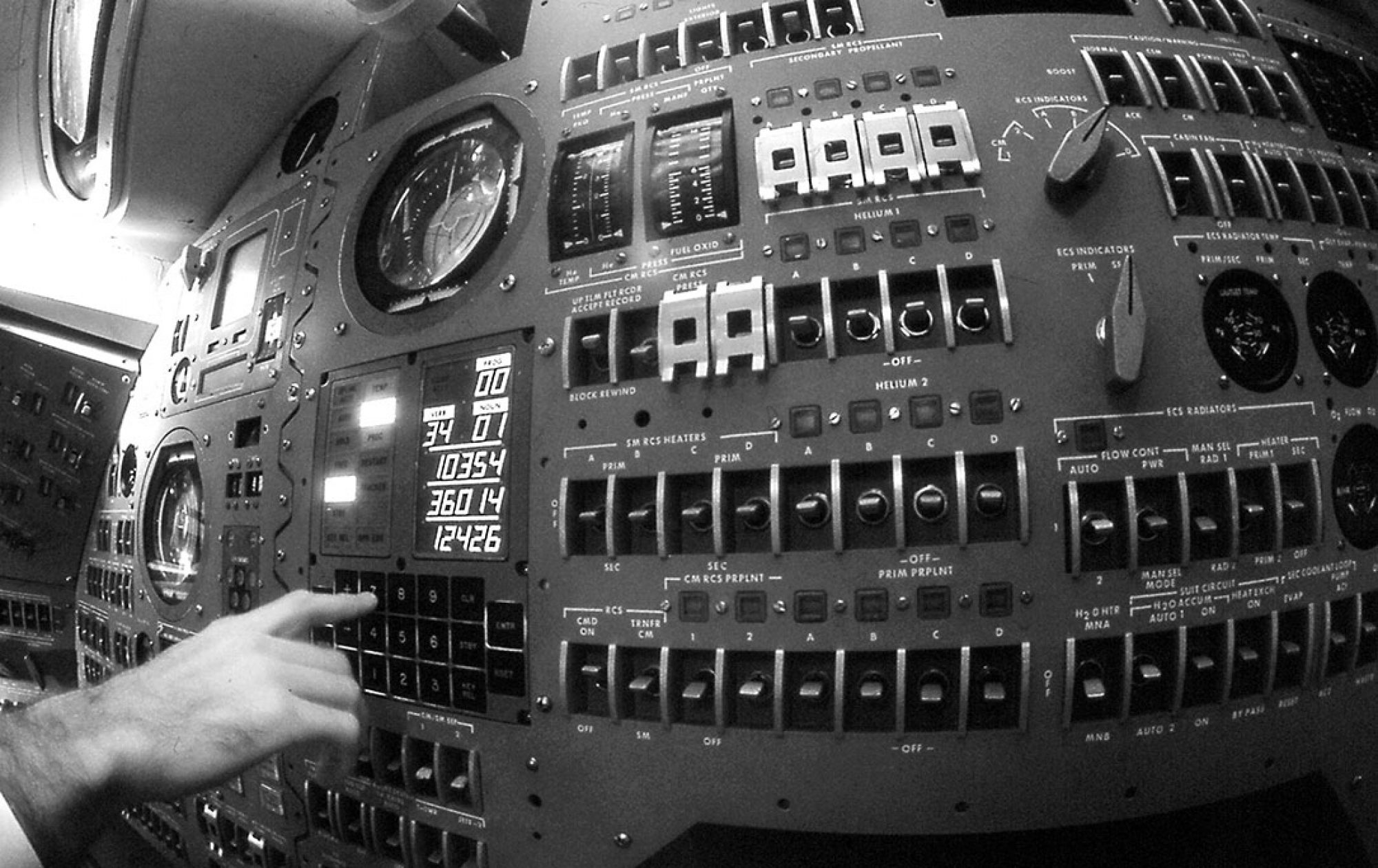

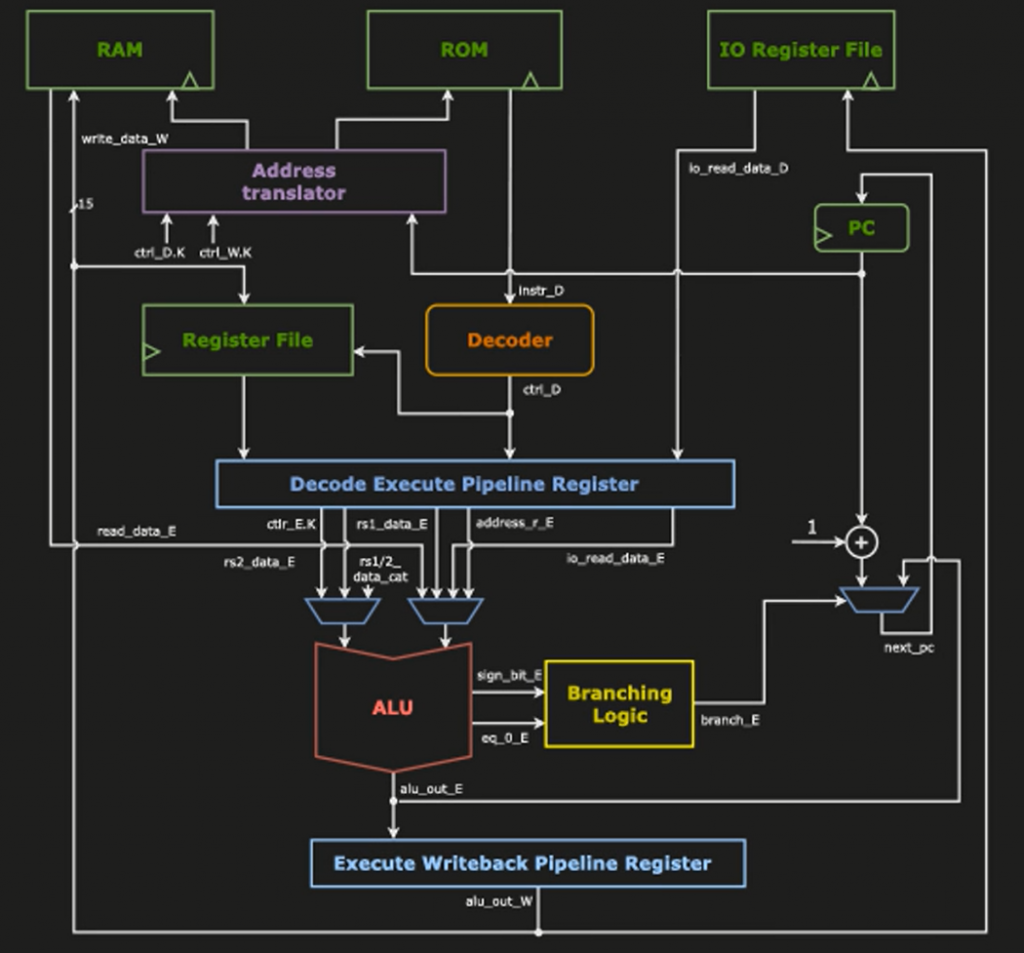

This week I spent most of my time catching a couple bugs in the implementation but mostly working on the video. I have decided that having some professional looking animations would help the audience comprehend some architecture level details (such as banked memory and the CPU pipeline) so I spent most of my time developing animations in After Effects. Below is a draft quality video of the CPU pipeline I animated. We are around 50% done with the video and I plan on getting more demo footage of the DSKY and completing the video by Monday/Tuesday. Wednesday and Thursday (after the Techspark Exposition) will be used for final preflight/pre-demo checks and some more bug hunting. We are very glad to have finished everything according to our plan and can focus on the video and the demo setup.

Team Status Report 4/30

The risk we worked on mitigating this week was not being able to effectively present our work. This week we finished up the presentation slides, and gave the presentation. In addition we made the poster and made a lot of the material for the video.

The video is being edited in Adobe After Effects, with elegant animations and transitions in an attempt to make the material as digestible as possible. Although very manually labor intensive, it provides professional visuals which will accompany our project.

We are done the presentation and the poster. Next week we will focus on updating the design report into the final report. We will also record and finish editing the final demo video. Lastly, we will attend the Tech spark Design Expo and final demo exhibitions.

Christopher’s Status Report 4/30

My task for this week was finishing the presentation, making the poster, and helping with the video. During the weekend (Sunday) I edited and polished the slides before we turned them in. I also held sole responsibility for the poster. So I made that. Lastly I helped with the video by making editing and polishing the diagrams relevant to the part of the project I implemented. I created or edited the memory map diagram, the ISA table, the pipeline diagram, and the tool chain diagram. Lastly I worked with Donny to write the script for the part of the videos which were relevant to the part of the project in which I worked on. We are on schedule with the poster finished and the video well under way. Next week I will be working apple video and the final report and demoing and presenting to the public.

Donovan’s Status Report 4/23

Last week, I performed additional verification of my UART receive_connector module as we were experiencing difficulty with comms. This revealed that my design was functioning as expected, but a few minor bugs with chip_interface were identified and corrected. Following that, I worked on getting up to speed on Jae’s work at the integration level, paying specific attention to the demo assembly program that our CPU runs. In anticipation of my upcoming presentation this week, I am generating slides and rehearsing to ensure effective timing.

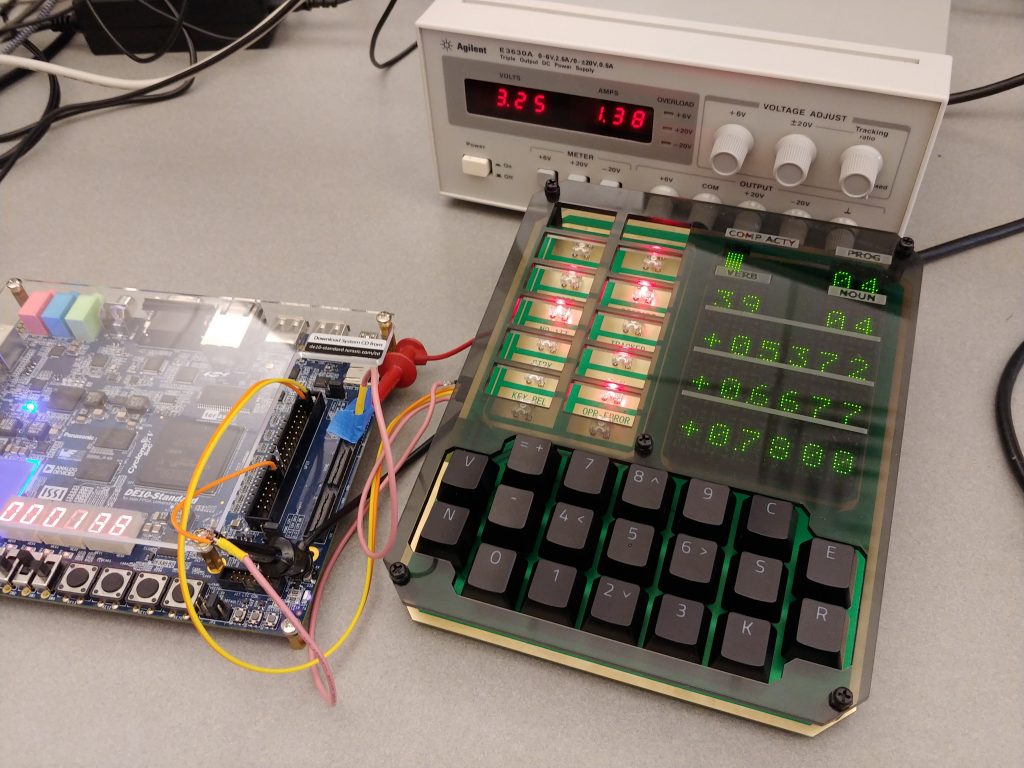

Jae’s Status Report 4/23

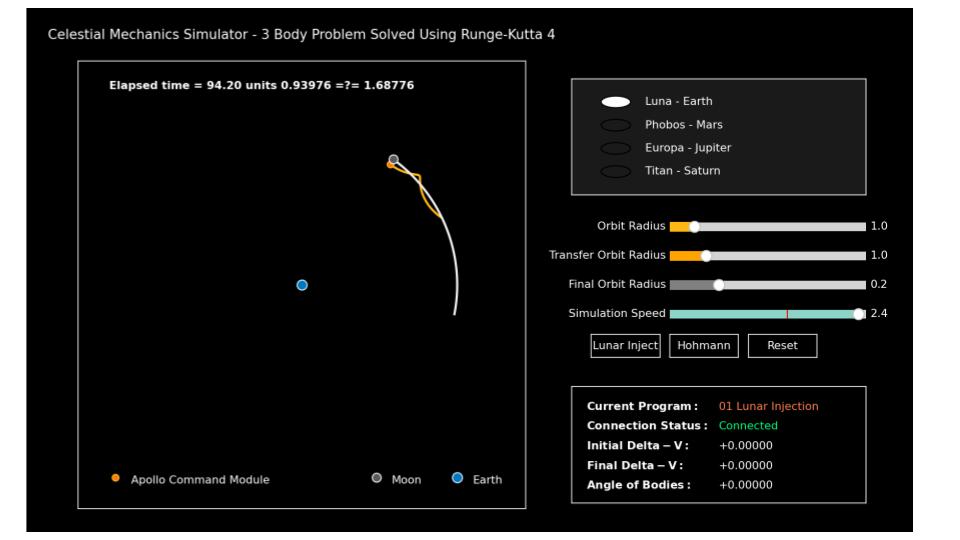

This was a very busy week of integration of the DSKY with the AGC and then with the demo software. Earlier this week, there were some obstacles getting RX and TX to work, but after their implementation the FPGA AGC was now running reliably. I was responsible for adjusting the DSKY firmware for integration with the AGC, which resulted in lots of unforeseen bugs, race conditions, and priority inversions with the ESP32 FreeRTOS. After majority of the bugs were fixed, I had to write our custom 3-body simulator (Runge-Kutta 4th order ordinary differential equation solver) and the interface to the ESP32 via wireless connection. Although some bugs remain, fortunately it is functional and therefore we have reached critical mass for our MVP demo.

My goal next week is to work on the video and further tune out the bugs in the ESP32 and the Python demo.

Team Status Report 4/23

The main risk we mitigated was not having a demo-able project. This week we finished integration between the FPGA AGC and the DSKY and ESP along with our laptop display. We then debugged our demo program on our working implementation or our project. It now works, the preliminary demos for escape velocity, orbital transfers (Hohmann Transfer), and Translunar injection have been verified to be correct using our custom 3-body simulator.

We also worked on the presentation this week also (as the presentation in next week) working on this entailed taking various metrics from our design such as the operating temperature of our DSKY the IPC of our AGC implementation and many other metrics. We then used this to make the presentation.

We are ahead of schedule now that we are done with the technical aspects of our project. Next week we will focus on the final report, poster, and demo video.

Christopher’s Status Report 4/23

My task for this week was integration and making the presentation. As far as integration went I was responsible for making sure the uart connection and io interface between our FPGA implementation of the AGC and the microcontroller worked (mostly on the FPGA side) and spend several hours debugging that. I also helped Jae with debugging the demo code once it was running on everything. Lastly I organized the work for the presentation and made several slides. To work on the presentation (particularly the quantitative testing slides) I had to write some code and take benchmarks of our design. We are more or less done with the technical component of our project (a week ahead of schedule). Next week I will be working on the poster and the apple video and the final report and whatever else we need to finish up the project.

Donovan’s Status Report 4/16

Earlier this week, I was working on producing a new division module that complied with the double precision format of the AGC architecture, as my previous design did not. Unfortunately, a few implementation details prolonged that work, and as a team, we decided that DV and DDOUBLE instructions would move lower on our list of priorities. Putting that aside, we shifted focus to our CPU’s UART interface, by which the I/O registers communicate with the outside world. I implemented and tested a module that receives an update stream for the CPU’s input registers, byte-by-byte, from a unit (courtesy of Ben Marshall on GitHub) that already handles receiving the data bit-by-bit. My unit then updates the CPU’s input registers as the data is received. We have begun the first leg of high-level integration and validation. Next week, I plan to assist in this process as well as prepare for the final presentation.