What did you personally accomplish this week on the project? Give files or photos

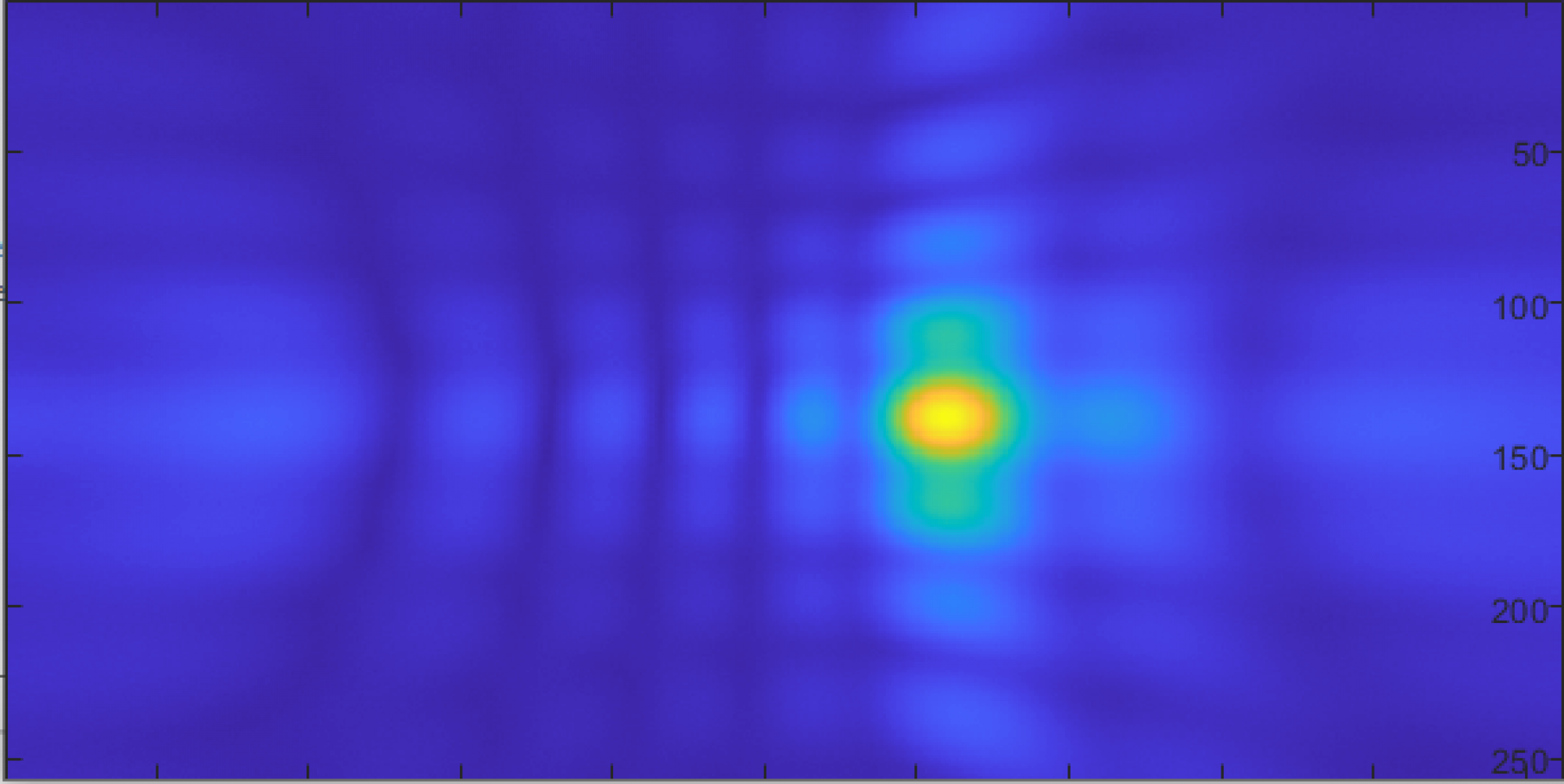

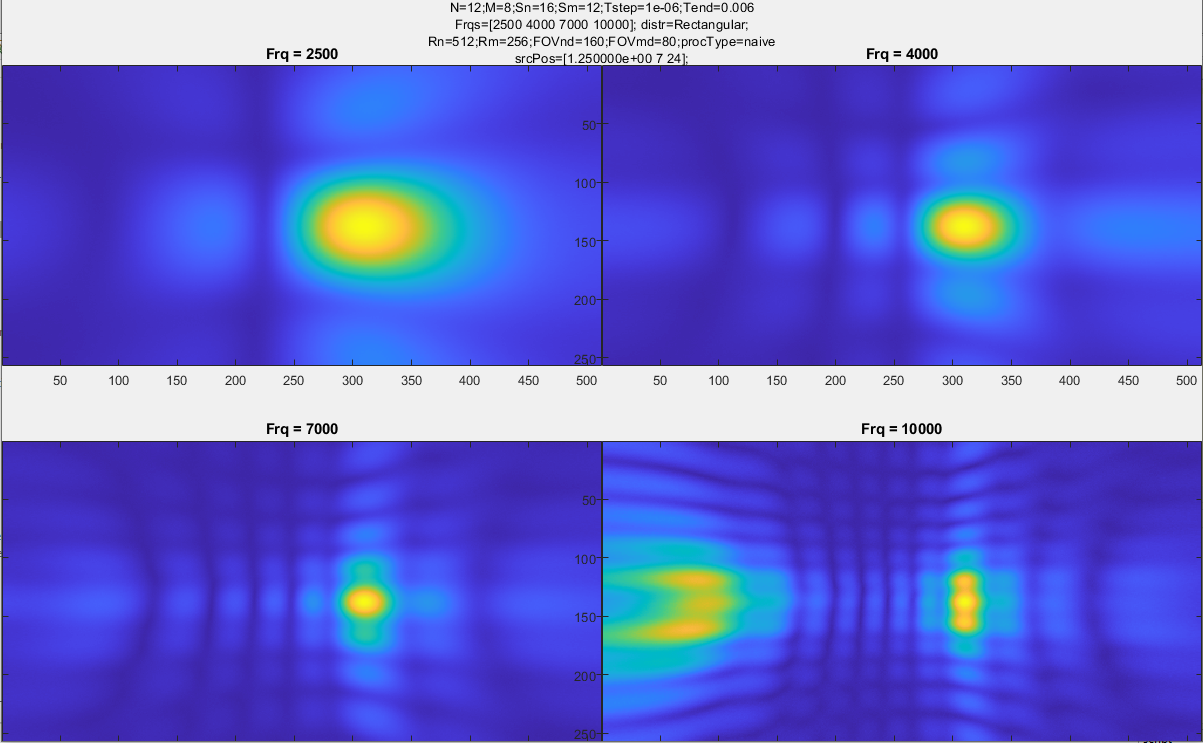

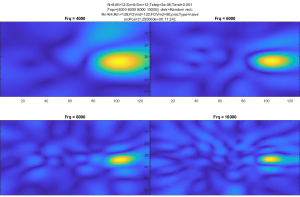

This week I mainly did simulations of different array geometries, microphone quantities, and spatial distributions. More of these images are in the team report, but a specific result of note is shown below:

This was a simulation of a single point source set to 4,6,8, and 10 KHz for each set of images, with a 8″x12″ array of 96 microphones. The upper set of 4 images shows a regular rectangular grid arrangement, and shows clearly visible repeated artifacts (sidelobes) that also appear in a similar grid pattern. The lower set of images shows microphones randomly distributed in the same space. In this case, the main lobes are essentially unchanged, but the distinct, repeated artifacts are replaced with a much more macroscopically uniform noise. The hope was, that removing the periodic spatial component of the array would spread out the sidelobes more evenly throughout the entire image. Since some areas in the first images have noise floor to spare, it seems that it may be possible to spread the artifacts out into these areas, reducing their peak amplitude at the expense making them larger spatially. The random distribution did spread out the artifacts almost completely evenly over the entire image, but, did not significantly reduce the peak amplitude, which was the whole point. We will likely take another look at doing something like this (altering geometry to reduce artifacts) later on in the project, but for now, we plan to move forward with the rectangular array of 96 microphones, as initially planned.

I also set up the xilinx toolchain for a board I already owned, which we plan to use to do some initial proof-of-concept testing for the gigabit ethernet interface. We expect that to be one of the more significant technical hurdles of the project, and want to get some experience with it before coming up with the final design. I didn’t have enough time to actually get the ethernet driver working, but, was able to, after some initial difficulties, program the fpga with a basic program.

With our change to primarily pursuing PDM microphones instead of analog microphones, several components of the plan have changed, but, we are still on track under the new plan.

This coming week, I plan to do some basic, proof of concept testing of the GbE interface, to make sure that it will work for our project before we fully commit to that. I also plan to begin design of the PCB to interface the FPGA board to the microphones, but I do not expect to finish it this week. If any of the microphones we’ve ordered show up within the week, I plan to begin some experiments and proof-of-concepts with those.