Commands:

Draw Rectangle

Create Pin

DRC

Extraction

LVS

Useful Virtuoso Commands

VIRTUOSO [TOP]

Cadence Virtuoso is used for the actual silicon layout of integrated circuits. It can perform several kinds of verification checks on your designs, including Design Rule Checks (called DRC, duh...) and Layout Versus Schematic checks (see if you can figure out the acronym). It also has the ability to create SPICE netlists from the layouts you create, should you wish to simulate your design.

Like most Cadence windows, Virtuoso has a menu along the top and a status area at the bottom. There is also a row of buttons for common functions along the left edge of the window. If you point the cursor at a button, a pop-up window will show the function it performs. In addition, it has a seperate Layer Select Window, which will pop up when you start Virtuoso. This window contains the layers you may use when laying out your circuit.

Virtuoso can operate in different modes, depending on the command(s) you enter. There is a mode for drawing rectangles, a mode for drawing pins, and so forth. You can tell which mode you are in by looking at the status line at the bottom of the window. It will tell you what action you can perform. The line above the status line will show the function of each of the three mouse buttons. These will be different in different modes.

You select the mode by choosing commands such as move, copy, add pin, etc. These commands are chosen from the menu. To copy something, you would first select Edit...Copy from the menu. Most commands also have a shortcut key as well. For the copy command, the shortcut key is c. Many commands will repeat until you cancel them. For instance, once you start drawing rectangles, Virtuoso will stay in draw rectangles mode until you tell it to stop. You can exit from a modal command by pressing the Esc key.

SAVING: You should save your layouts frequently by selecting Design...Save from the menu or by clicking on the save icon.

CLOSING: To close the Virtuoso window, select Window...Close from the Virtuoso menu.

Draw Rectangle

[TOP]

Shortcut: r

This command is used to draw rectangles. After pressing r, you must select the layer you want from the Layer Select Window, shown below:

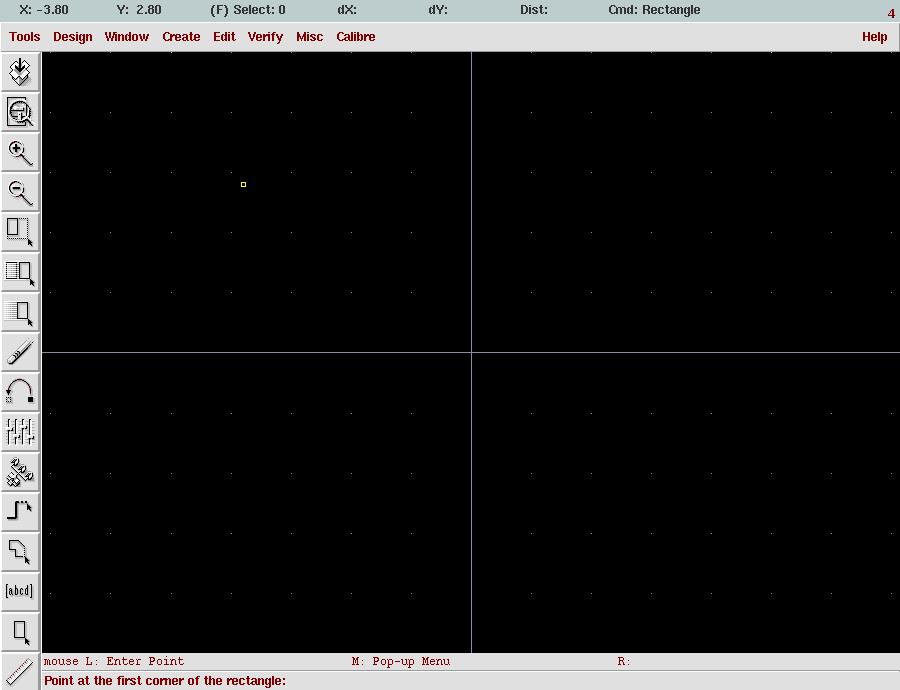

After selecting the layer you want, click the left mouse button in the layout window where you want to place one corner of the rectangle:

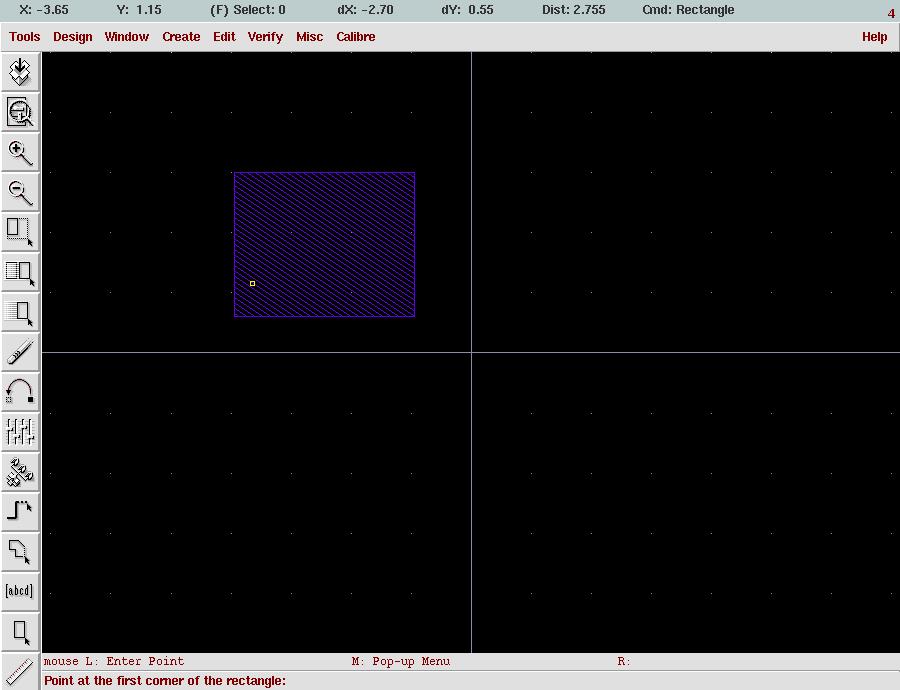

Then, click the left mouse button where you want the opposite corner to be placed:

This gives you your rectangle:

Create Pin [TOP]

Shortcut: CTRL-p

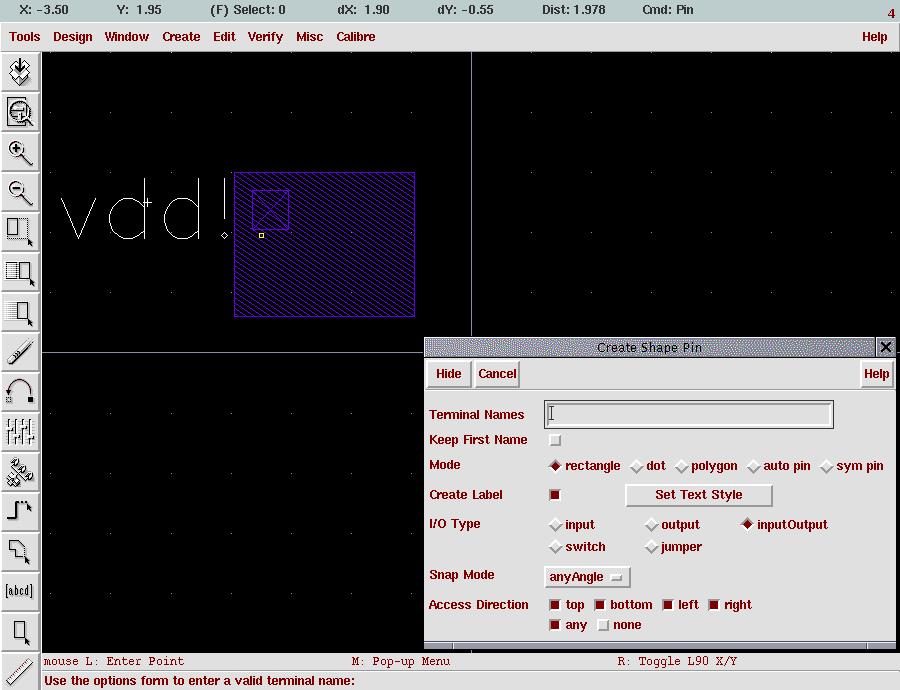

In the Create Pin window, select Shape pin, and then select the appropriate pin drawing layer from the LSW (one of the layers labeled pn). Give the pin a name, click on Create Label, and then draw a rectangle which will become the pin, and then place the label. The rectangle MUST be drawn over a layer of the same type - e.g., if you wish to make a pin in metal1, you must have a metal1 layer underneath where you want to create the pin:

Design Rule Checker [TOP]

The Design Rule Checker's function is to ensure that your layout conforms to the physical limitations of the process you are using (in this case, HP's 0.35u process). It makes sure that you have not created structures in your design which cannot be re-created on silicon. Note that unlike some other tools used previously in this class (MAGIC, for example), Virtuoso does not perform DRC in real-time. Hence, it is advisable to run DRC frequently, especially when you are not familiar with the design rules of a particular process.

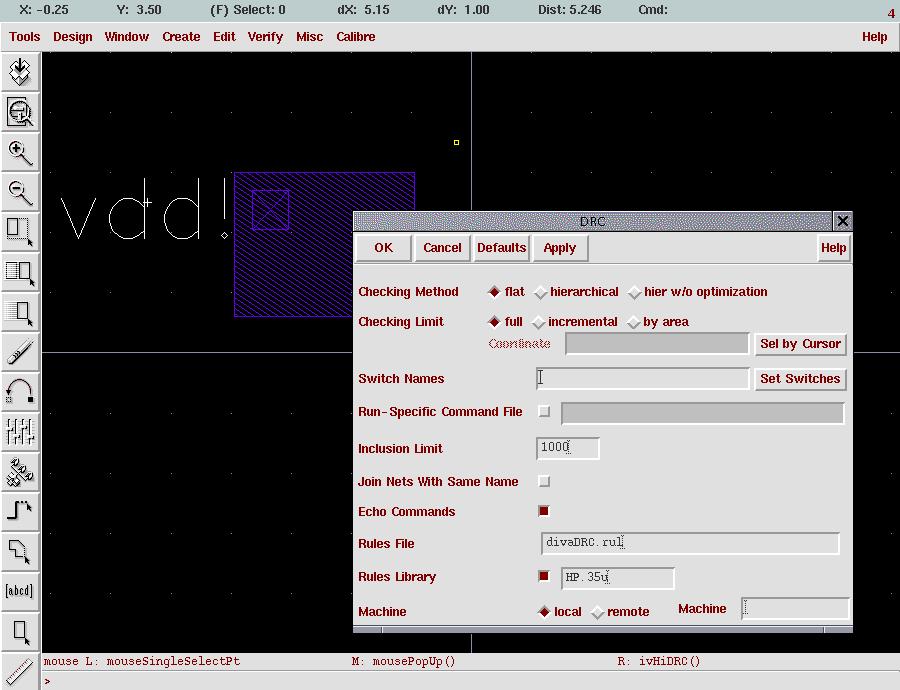

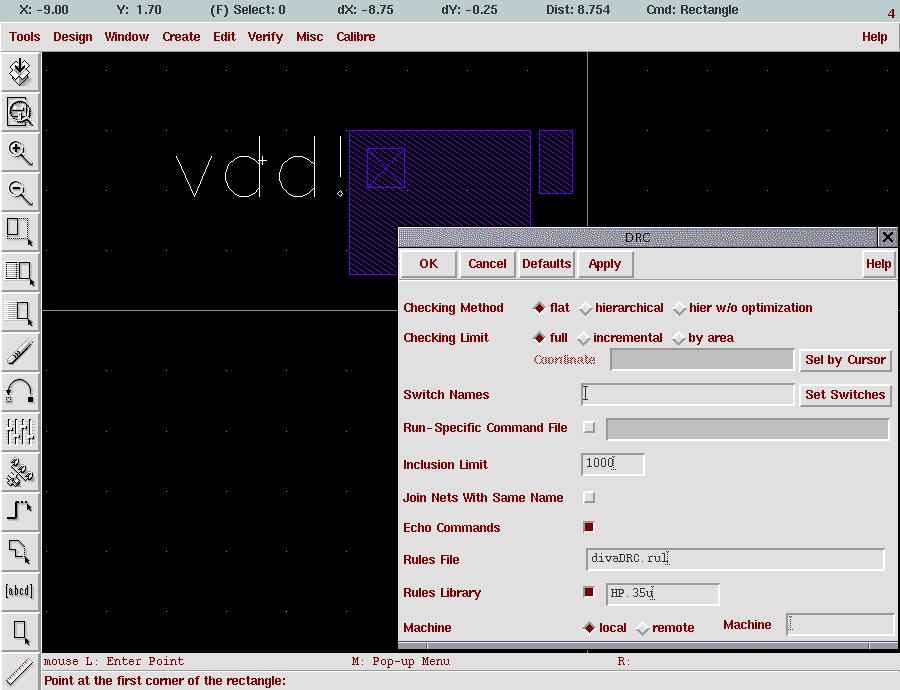

To perform DRC, go to the Verify menu, and select DRC. This will bring up the following window:

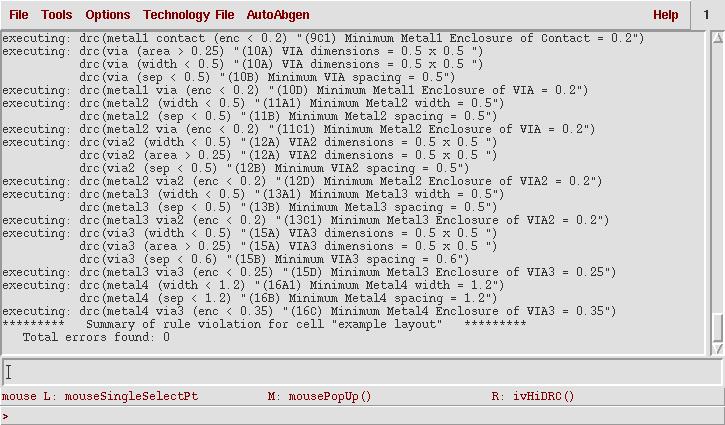

Leave all the default settings, and press Ok. This will start the Design Rule Checker. You will notice many lines scrolling past in the Command Information Window as Cadence checks each rule. Finally, it will print a summary of the number of errors and warnings, if there are any:

As you can see, in this case, there aren't any errors. Let's take the case of a layout which does produce an error, such as this one:

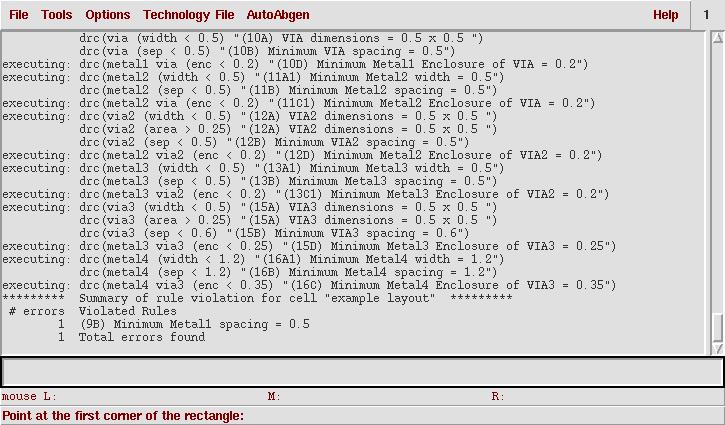

After running DRC, we see the following output on the Command Information Window:

Also, the layout now has a small white area on it, which represents the error:

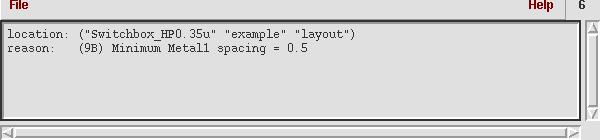

To find out what the error is, select Markers->Explain from the Verify menu. Then, click on the white area, and Virtuoso will pop up a window detailing the problems in that particular area:

Extraction

[TOP]

Useful Virtuoso Commands [TOP]

Editing Commands:

r - Draw Rectangle Mode

CTRL-p - Create Pin

DEL - Delete

m - Move

s - Stretch

ESC - Clears selected commands

CTRL-a - Select All

CTRL-d - De-Select All

Zoom Commands:

f - Snaps the entire design into focus on the layout window

CTRL-Z - Zoom in by a factor of 2

SHIFT-Z - Zoom out by a factor of 2

z - Zoom to box (select on layout window)

![]()