What did you personally accomplish this week on the project? Give files or photos that demonstrate your progress. Prove to the reader that you put sufficient effort into the project over the course of the week (12+ hours).

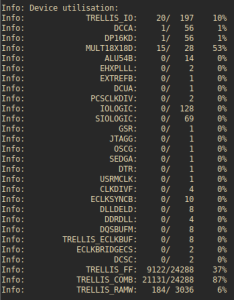

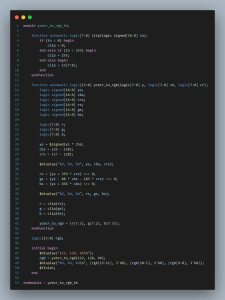

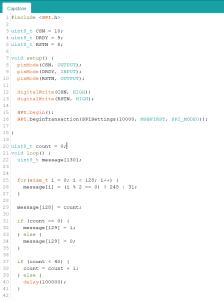

At this point almost everything works together. We were able to transmit an image from the remote node all the way through the pipeline to the display. I’ve deferred the image of this working to the team status report. To get this stage included a bit of bug fixing. I made some mistakes when it came to clock doman crossing and was able to sort that out.

Is your progress on schedule or behind? If you are behind, what actions will be

taken to catch up to the project schedule?

I am on track right now. We were able to do some real world testing today and should be able to finish everything up!

What deliverables do you hope to complete in the next week?

I hope to have everything done. Including increasing the processing speed of the decoder and the display driver. I realized that its a little too slow right now to hit the 6 streams @ 10fps target but I am pretty close to getting it all sorted out.

As you’ve designed, implemented and debugged your project, what new tools or new knowledge did you find it necessary to learn to be able to accomplish these tasks?

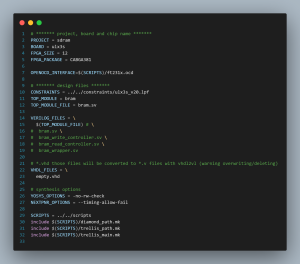

I learnt quite a few new things putting this project together. Some of the new tools that I got very familiar with was a new vendor of FPGA devices (Lattice) and all the quirks that come with it. Using open source tools meant that some of the features that alternatives like Xilinx or Altera had (such as a platform builder to get IPs integrated) simply didn’t exist. I had to do more manual methods of getting things up and running.

What learning strategies did you use to acquire this new knowledge?

As for most things, the way I was able to learn these things was just by doing it! I was able to hunker down and just figure things out and was able to learn a lot during the process.