Earlier this week, I assisted Christopher in debugging our CPU implementation to work with multiplication, division, augment, diminish, and increment instructions. Although we reached a consensus that these instructions were working, we’ve discovered recently that our double-precision computations don’t work the same way as the yaYul simulator implementation. For cleanliness, we have decided to forego changing our multiplier and divider circuits as well as adding a double precision adder. I am currently writing those implementations in SystemVerilog in anticipation of verifying their correctness with example assembly programs. These changes will allow us to implement a CPU that meets the capabilities of our desired demo programs. Following these changes, I will make updates to the I/O “register file” to support Jae’s desired I/O format, then implement the I/O serial interface.

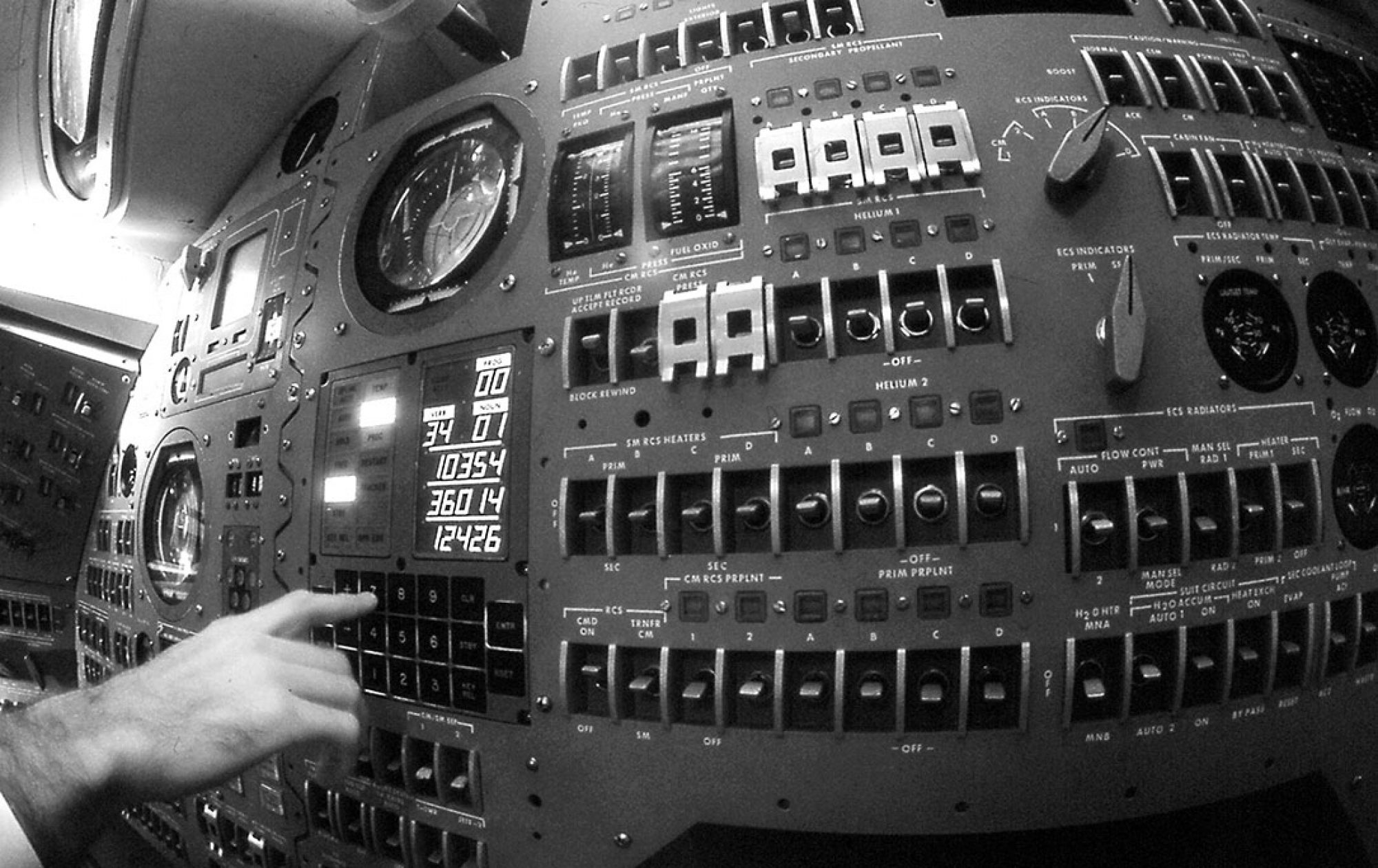

Bringing the Apollo Guidance Computer to the 21st century