I switched gears a bit this week, and first began gaining familiarity with Quartus’s IP Megafunction generator. Using the Intel manuals I had recently browsed, Christopher and I configured and procured the Verilog files for our block RAM. We are currently unsure of how exactly we want to register the RAM ports, but we plan to explore this later next week. Most of my work this past week involved writing modules in SystemVerilog for our mostly one’s complement ALU. The one’s complement adder/subtractor with end-around-carry correction has been written. I realized that signed multiplication/division in one’s complement would be quite time-consuming to develop, so I decided to configure a combinational multiplier using the LPM_Mult megafunction in Quartus. Because this is a two’s complement multiplier, I also wrote modules to convert between the two forms. These are instantiated at the ports of the LPM_Mult multiplier. All written modules still have yet to be verified.

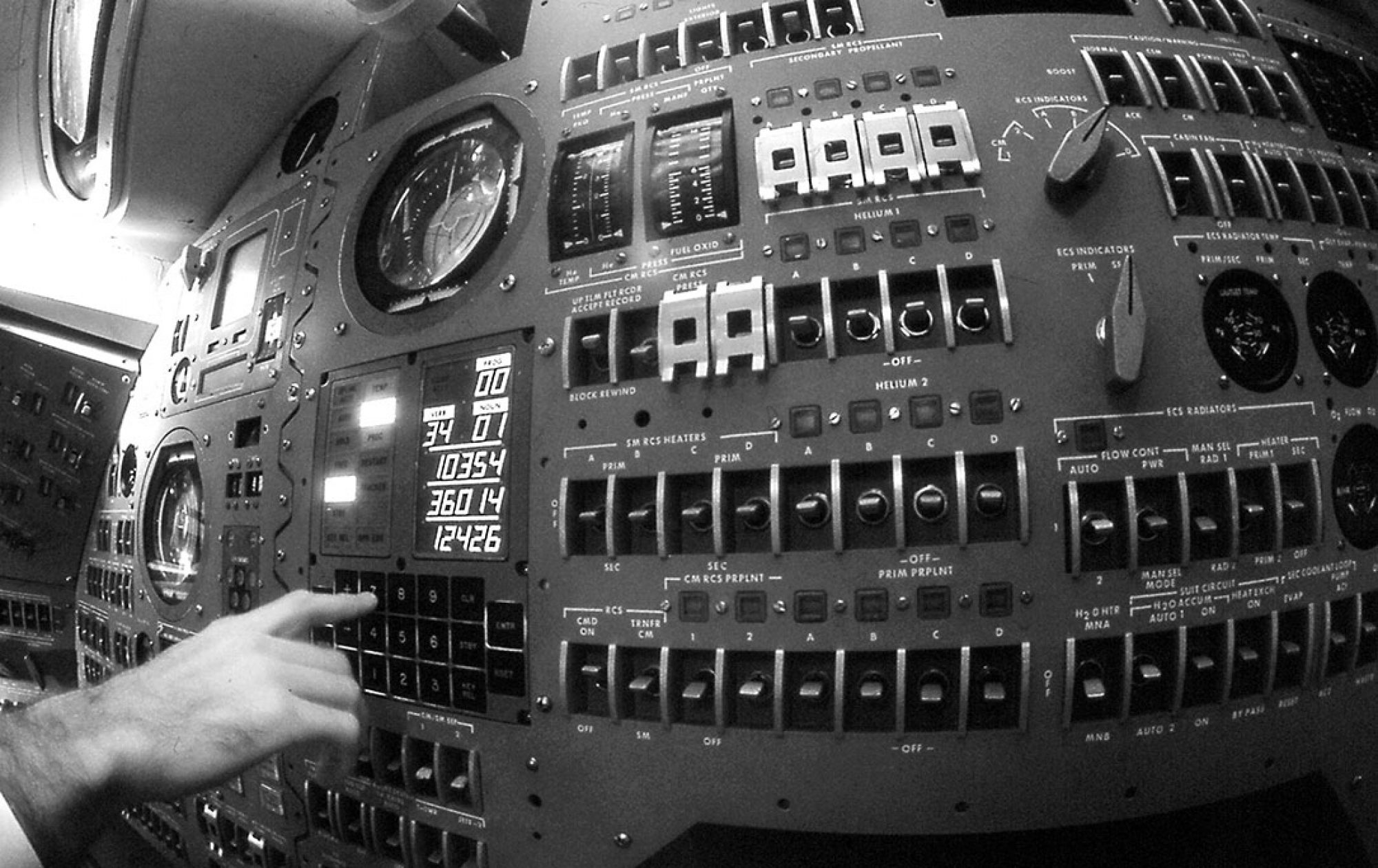

Bringing the Apollo Guidance Computer to the 21st century