This week we were dealing with a few significant risks. The first one was the worry that our PCB would not be ready in time. In order to deal with that we started the layout this week and aim to be done with the preliminary layout in the coming week. Another risk was going into our project without knowing how to do every step and realizing some steps were much harder than we thought. We minimized this risk by doing more research into some of the details of our project so we could have a better idea about our implementation and it’s feasibility

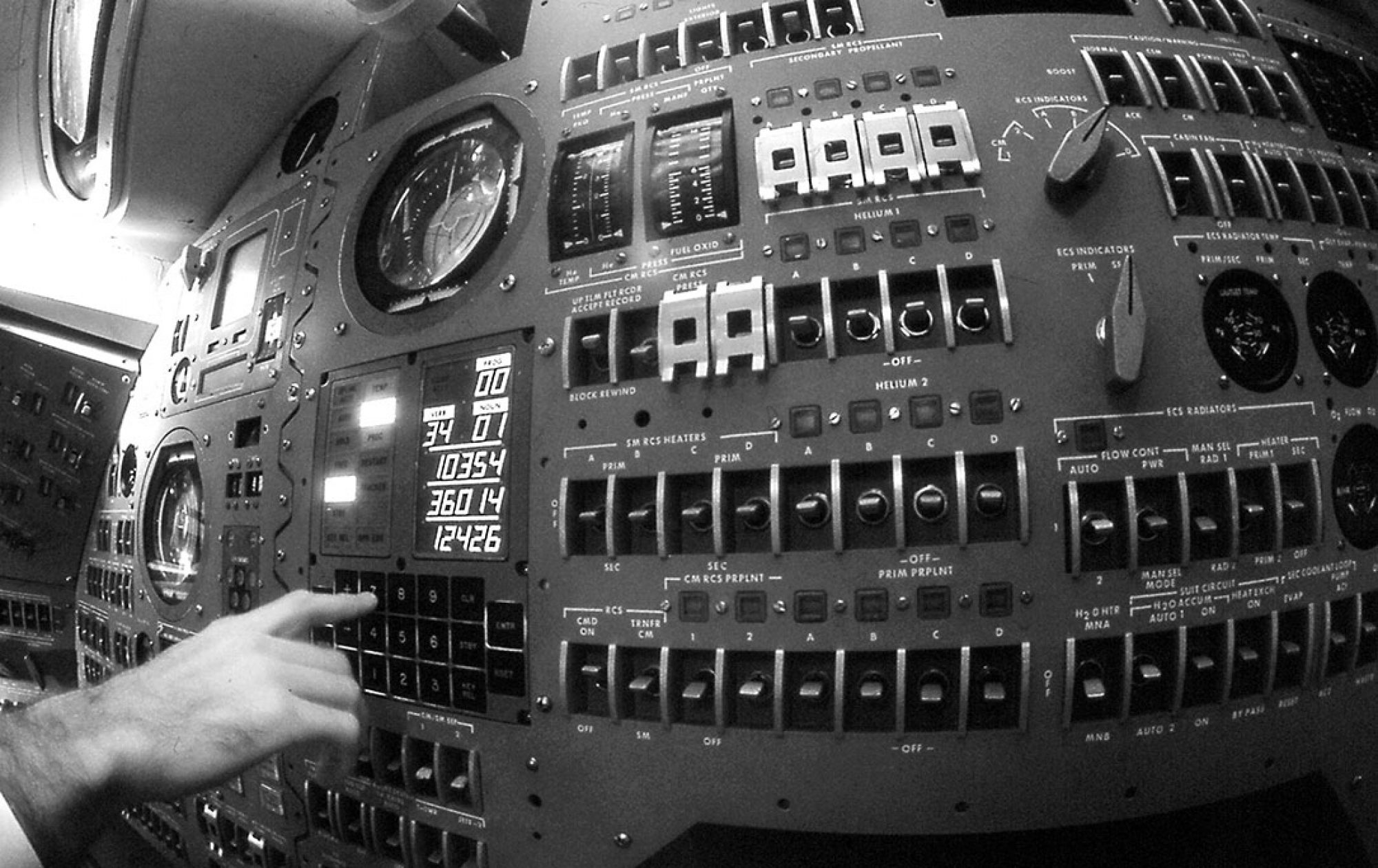

We made some changes to the use case. Our use case is now a museum rather than for actual space travel. We made this change on the recommendation of our advisor. This changes a few things about our project. Firstly we are implementing more of the instruction set to stay more true to the original design. This will increase the difficulty of the cpu pipeline design and implementation (which will consume more time), but it does mean we will be able to use more of the original Apollo programs which will hopefully save us some time.

We started our PCB layout earlier than expected so our schedule now looks like this

A sneak preview of the schematic capture:

A link to our current cpu design is here https://app.diagrams.net/#G1K-aGTft1UyUYiGw6LQ5oJ6zeiqgNk8Xc