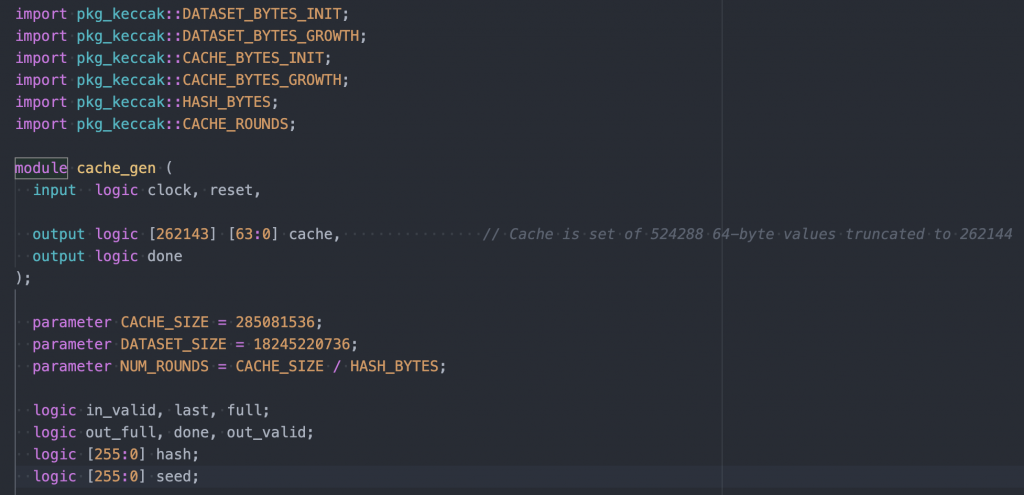

This week I continued working on the Ethereum mining modules and almost have the cache and dataset generation complete. One issue I ran into was the FPGA not having enough memory to store the full 1GB dataset size. I am attempting to solve this problem by only storing the 16MB cache and generating dataset entries as needed. Although calculating dataset entries as we go along will take longer than pre-generating it, this seems to be the only solution as of now. I also researched more about ethash and the hashimoto algorithm that it uses. Although there are some speed optimizations that others use between a light hashimoto and a full hashimoto, we are limited by memory to only the light hashimoto. This version only uses the cache and not the dataset.

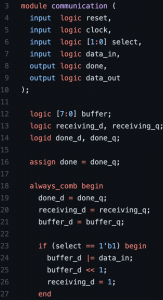

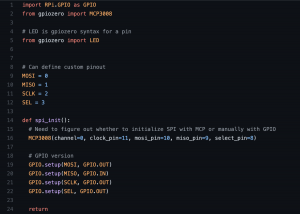

I am slightly behind on finishing the Ethereum implementation. I spent the past week having to help Lulu debug the Raspberry Pi communication while also generating configuration files for the team to test the GPIO sending and receiving. Although I anticipate being able to finish the Ethereum component on time, I am unable to fully test receiving puzzles and sending nonces without the Raspberry Pi communication up and running. That is still the biggest bottleneck of this project.

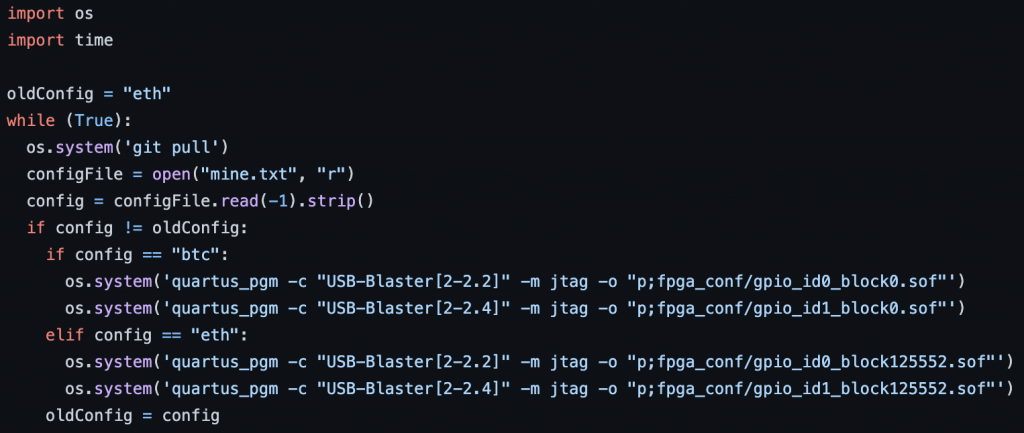

Next week we will be presenting our project at the Final Demo on Friday so I will have the Ethereum mining modules working as intended. If communication still does not work at that point, I will resort to running them on preset puzzles like I am doing for Bitcoin. The FPGA configuration switching will be operational with the decision tree portion of the project.