I continued to debug the Ethereum mining code along with the associated SystemVerilog communication modules. I looked into the source of the issues and found out that Ethereum requires a cache size of 32 MB along with an ever changing dataset size. The current dataset is about 2.78 GB which should fit on the SD cards that we bought. I am using this information to hash the Ethereum puzzle to compare against its target.

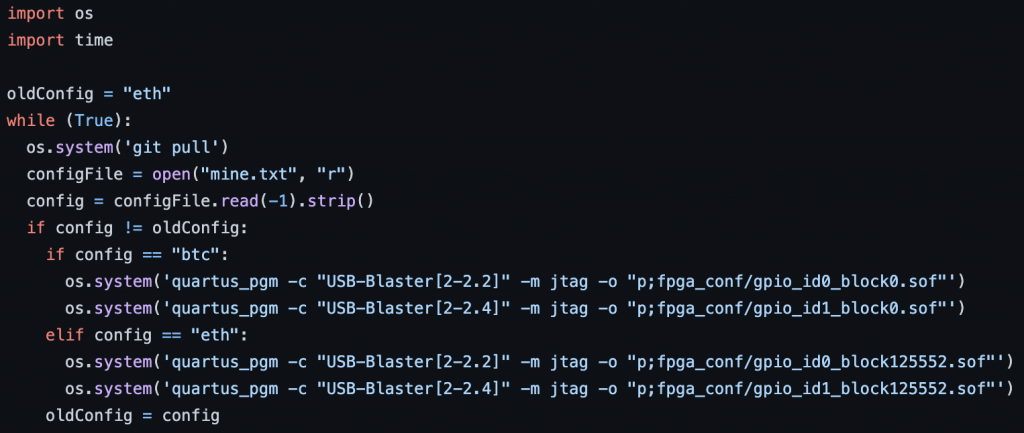

Another issue we ran into was getting the configuration switching time low enough to meet our requirement of 10 seconds. Quartus Programmer loads the boards sequentially even when given the command simultaneously so I researched using threads and other concurrency tools to lower our switching time. After talking with David, the solution we came up with was to change the way the cryptocurrency spread was updated to only change one board at a time.

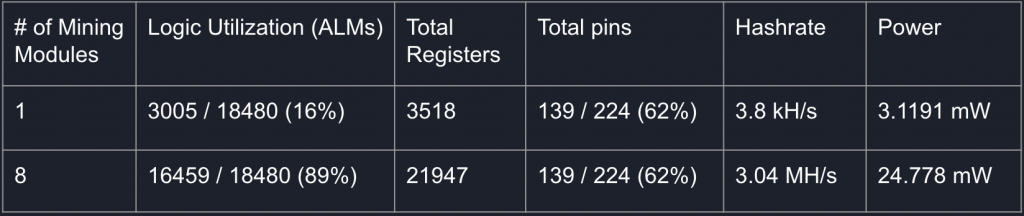

I did more metric testing this week by getting the cell area, power, and hash rates of our system running with one mining module vs. multiple mining modules. I then used this data to calculate our expected returns. With this information, I plan to work on optimizing our design next week so that we are able to generate higher returns.

I am on track with my schedule but still running into issues with testing my part of the project with the Raspberry Pi portion. Lulu is working on getting the sending and receiving code to work so I am waiting for that to finish before I can fully test the communication modules of the FPGA.