# 18-344 Recitation 2

09/12/2025

#### Outline

- 1. Logistics

- 2. Review

- 3. Labs

- a. Lab 0

- b. Lab 1

#### Logistics

- Lab 0 due September 15 (next Monday) (in 3 days)

- Review last week's recitation if needed

- Homework 1 due September 14 (Sunday) (in 2 days)

- Covers materials from lectures 1-4

- NEW Lab 1 will be released on September 15 (next Monday) (in 3 days)

- From lab 1 onwards, all labs will be *partnered (group of 2 unless otherwise approved)*.

Start looking for a lab partner now!

- Use the Piazza post and/or Slack to find your lab partner.

# Review

### Speedup

$$S = \frac{t_{\text{base}}}{t_{\text{improved}}}$$

### Speedup w/ Example

When we say: A is X times faster than B, we mean:

$$X = \frac{T_B}{T_A}$$

### Speedup w/ Example

"You friend proposes an optimization which would speed up *all* operations by 30%"

$$X = 1.3 = \frac{T_{\text{original}}}{T_{\text{optimized}}}$$

### ISA Design

ISA is the contract between hardware and software. It's what the hardware offers and what the software would expect to be available.

If something is not necessarily required to be known by **both** hardware and software, it shouldn't be in the ISA<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup> Exceptions<sup>2</sup> apply.

<sup>&</sup>lt;sup>2</sup> These exceptions are out of the scope of this class.

### So, what's usually in an ISA?

- Architectural registers

- e.g. x0 ... x31 in RISC-V's RV32/RV64 ISAs

- Instruction definitions

- o e.g. ADD, XOR, LOAD, STORE, etc.

- Definitions include:

- What the operation and operands are

- What the side-effects are

- How the instruction should be encoded

#### Memory

More specifically, the idea of *the existence of memory*.

- The ISA defines how large the memory address space is, and how to use the memory.

- e.g. RV32I has a byte-addressable memory address space of 2^32 bytes.

Aside: RISC-V instruction syntax

```

opcode rd, rs1, rs2 \Rightarrow rd = op(rs1, rs2)

```

opcode rd, rs1, imm  $\Rightarrow$  rd = op(rs1, imm)

... for more, check out

https://github.com/riscv/riscv-isa-manual/

### So, what's usually *not* in an ISA?

#### Microarchitectural registers

i.e. Physical register files used to implement architectural registers are not in the ISA.

#### • Instruction *implementation*

- e.g. It is 100% valid for the implementation of an ISA to choose to use a single adder to implement MUL, as long as the result of the MUL adheres to what the ISA defines.

- e.g. It is also 100% valid for the implementation of an ISA to choose to use a slow adder for some ADDs and a faster adder for other ADDs under different circumstances<sup>1</sup>.

#### What memory is made of

- e.g. ISA doesn't tell you how much physical memory is available.

- e.g. ISA doesn't specify how much time it takes to write to/read from memory.

<sup>&</sup>lt;sup>1</sup> This is true as long as all the ADDs are using the same instruction and the ISA does not specify instruction latencies<sup>2</sup> (whether cycles or wall-plug time).

<sup>&</sup>lt;sup>2</sup> For this course, we assume that ISAs don't specify instruction latencies.

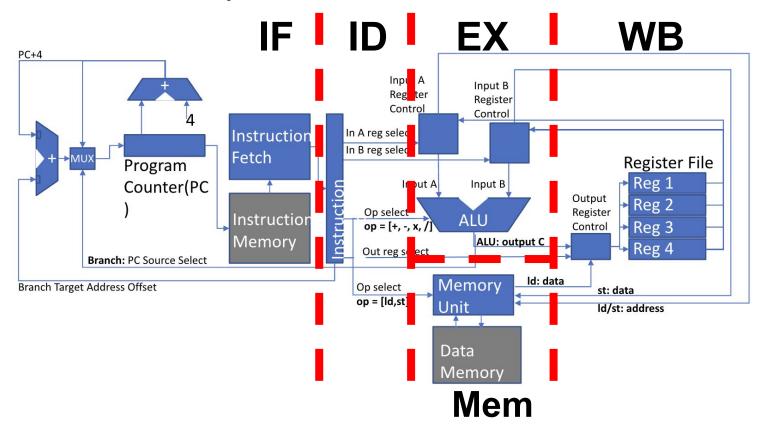

#### Basic RISC-V Datapath

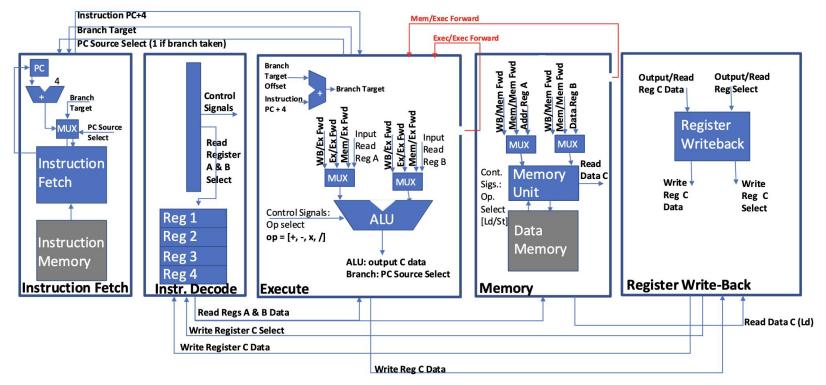

# 5-Stage Pipelined Processor Datapath a.k.a. The 5-Stage Pipeline

with Branch Prediction and EX->EX & Mem->EX Forwarding

#### **WITHOUT EX->EX** & Mam SEV Forwarding

| o otage i ipelifica Execution |                |    | Welli->EX FC | orwarding |    |

|-------------------------------|----------------|----|--------------|-----------|----|

| Cycle                         | IF             | ID | EX           | Mem       | WB |

| 1                             | lw x1,0×10(x0) |    |              |           |    |

|                               |                |    |              |           |    |

|                               |                |    |              |           |    |

|  | I . | I . |  |

|--|-----|-----|--|

### E Ctoro Dinalinad Execution

addi  $x2, x1, 0 \times 1$  | lw  $x1, 0 \times 10(x0)$

# **WITHOUT EX->EX &**

| 5-    | 5-Stage Pipelined Execution |    |    | Mem->EX Fo | orwarding |

|-------|-----------------------------|----|----|------------|-----------|

| Cycle | IF                          | ID | EX | Mem        | WB        |

| 1     | lw x1,0×10(x0)              |    |    |            |           |

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

$lw x1,0 \times 10(x0)$

addi x2,x1,0×1

# **WITHOUT EX->EX &**

| 5-Stage Pipelined Execution |                |    | Mem->EX Fo | orwarding |    |

|-----------------------------|----------------|----|------------|-----------|----|

| Cycle                       | IF             | ID | EX         | Mem       | WB |

| 1                           | lw x1,0×10(x0) |    |            |           |    |

$lw x1,0 \times 10(x0)$

# WITHOUT FX->FX &

| 5-Stage Pipelined Execution |                |                | on             | Mem->EX Fo |    |

|-----------------------------|----------------|----------------|----------------|------------|----|

| Cycle                       | IF             | ID             | EX             | Mem        | WB |

| 1                           | lw x1,0×10(x0) |                |                |            |    |

| 2                           | addi x2,x1,0×1 | lw x1,0×10(x0) |                |            |    |

| 3                           | add x3,x2,x1   | addi x2,x1,0×1 | lw x1,0×10(x0) |            |    |

| _                           |                |                |                |            |    |

addi  $\times 2$ ,  $\times 1$ ,  $0 \times 1$  | lw  $\times 1$ ,  $0 \times 10$  (x0)

addi references a value in x1, but the previous lw has not yet put a new value in x1 yet!

# <u>WITHOUT</u> EX->EX & Mem->EX Forwarding

| Cycle | IF             | ID                            | EX             | Mem            | WB |

|-------|----------------|-------------------------------|----------------|----------------|----|

| 1     | lw x1,0×10(x0) |                               |                |                |    |

| 2     | addi x2,x1,0×1 | lw x1,0×10(x0)                |                |                |    |

| 3     | add x3,x2,x1   | addi x2,x1,0×1                | lw x1,0×10(x0) |                |    |

| 4     | add x3,x2,x1   | addi x2, <mark>x1</mark> ,0×1 | 1              | lw x1,0×10(x0) |    |

|       |                |                               |                |                |    |

|       |                |                               |                |                |    |

Solution: insert a pipeline bubble in the EX stage to force the addi to wait until x1 has the new value. In practice people use the nop instruction or clear the control signals to create the pipeline bubble. We also call this "stalling the EX stage".

addi  $x2, x1, 0 \times 1$

addi  $x2, x1, 0 \times 1$

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

add x3, x2, x1

5

# WITHOUT EX->EX & Mem->EX Forwarding

$lw \times 1,0 \times 10(\times 0)$

$lw x1,0 \times 10(x0)$

| 5-Stage i ipelifica Execution |                |                | Wem->EX FC | orwarding |    |

|-------------------------------|----------------|----------------|------------|-----------|----|

| Cycle                         | IF             | ID             | EX         | Mem       | WB |

| 1                             | lw x1,0×10(x0) |                |            |           |    |

| 2                             | addi x2,x1,0×1 | lw x1,0×10(x0) |            |           |    |

$lw x1,0 \times 10(x0)$

Another pipeline bubble in the Mem stage is

also needed because x1's content won't be

updated until the end of the WB stage.

add x3, x2, x1

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

5

6

# WITHOUT EX->EX &

$lw \times 1,0 \times 10(\times 0)$

$lw x1,0 \times 10(x0)$

| 5-Stage Pipelined Execution |                |                | on | Mem->EX Forwarding |    |  |

|-----------------------------|----------------|----------------|----|--------------------|----|--|

| Cycle                       | IF             | ID             | EX | Mem                | WB |  |

| 1                           | lw x1,0×10(x0) |                |    |                    |    |  |

| 2                           | addi x2,x1,0×1 | lw x1,0×10(x0) |    |                    |    |  |

and Discilled at Essay at the sa

addi  $x2,x1,0\times1$

addi  $x2, x1, 0 \times 1$

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

$lw x1,0 \times 10(x0)$

addi  $x2,x1,0\times1$

The addi is cleared to proceed once x1 has been updated (lw

passes the WB stage). Note that pipeline bubbles also proceed.

# **WITHOUT EX->EX &**

$lw x1,0 \times 10(x0)$

| 5-Stage Pipelined Execution |                |                       | Mem->EX Fo                                                                                           | orwarding        |    |  |  |  |

|-----------------------------|----------------|-----------------------|------------------------------------------------------------------------------------------------------|------------------|----|--|--|--|

| Cycle                       | IF             | ID                    | EX                                                                                                   | Mem              | WB |  |  |  |

| 1                           | lw x1,0×10(x0) |                       |                                                                                                      |                  |    |  |  |  |

| 2                           | addi x2,x1,0×1 |                       |                                                                                                      | x2, but the prev |    |  |  |  |

| 3                           | add x3,x2,x1   |                       | has not yet put a new value in x2 yet! Also, note that add's reference to x1 won't be an issue here. |                  |    |  |  |  |

| 4                           | add x3,x2,x1   | <u>add1 /2,/1,0/1</u> | Weil to dilliood                                                                                     | CW /1,0~10(//0/  |    |  |  |  |

|                             |                |                       |                                                                                                      |                  |    |  |  |  |

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

5

6

add x3, x2, x1

addi x2, ≥ 1,0×1

addi  $x^2, x^1, 0 \times 1$

4

5

6

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

addi x2,x1,0x

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

# WITHOUT EX->EX &

lw  $\times 1$ ,  $0 \times 10(\times 0)$

| 5-otage i ipelifica Executio |                |                | Mem->EX Forwarding |               |    |

|------------------------------|----------------|----------------|--------------------|---------------|----|

| Cycle                        | IF             | ID             | EX                 | Mem           | WB |

| 1                            | lw x1,0×10(x0) |                |                    |               |    |

| 2                            | addi x2,x1,0×1 | lw x1,0×10(x0) |                    |               |    |

| 3                            | add x3,x2,x1   | addi x2,x1,0   | olution: more nin  | eline hubbles |    |

Solution: more pipeline bubbles...

addi  $x^2, x^1, 0 \times 1$

addi  $x2, x1, 0 \times 1$

4

5

6

8

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

addi x2,x1,0x

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

add x3, x2, x1

# <u>WITHOUT</u> EX->EX & Mem->EX Forwarding

$lw \times 1,0 \times 10(\times 0)$

addi  $x^2, x^1, 0 \times 1$

| 5     | 5-Stage i ipelified Execution |                |                   | Wem->EX F     | orwarding |

|-------|-------------------------------|----------------|-------------------|---------------|-----------|

| Cycle | IF                            | ID             | EX                | Mem           | WB        |

| 1     | lw x1,0×10(x0)                |                |                   |               |           |

| 2     | addi x2,x1,0×1                | lw x1,0×10(x0) |                   |               |           |

| 3     | add x3,x2,x1                  | addi x2,x1,0   | olution: more pin | olino bubblos |           |

addi  $x2, x1/0 \times 1$

addi

≥, x1, 0×1

3

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

add x3, x2, x1

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

add x0, x0, x0

4

5

6

8

9

# WITHOUT EX->EX &

addi  $x^2, x^1, 0 \times 1$

tw x1, v x v (x0)

addi  $x^2, x^1, 0 \times 1$

| J-    | Stage Fipeli   | IIIEU LAECUU   | OH | Mem->EX Fo | orwarding |

|-------|----------------|----------------|----|------------|-----------|

| Cycle | IF             | ID             | EX | Mem        | WB        |

| 1     | lw x1,0×10(x0) |                |    |            |           |

| 2     | addi x2,x1,0×1 | lw x1,0×10(x0) |    |            |           |

addi x2,x1, Same deal as before, add is allowed to

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

addi x2,x1, proceed once x2's value has been updated.

#### WITHOUT EX->EX & Mom->EY Forwarding

addi  $x^2, x^1, 0 \times 1$

TW X1, UXIU (X0)

addi  $x^2, x^1, 0 \times 1$

| •     | o otago i ipomioa Exocation |       |            |                                         | MEIII-/EX FC       | nwarumg  |  |

|-------|-----------------------------|-------|------------|-----------------------------------------|--------------------|----------|--|

| Cycle | IF                          | ID    |            | EX                                      | Mem                | WB       |  |

| 1     | lw x1,0×10(x0)              |       |            |                                         |                    |          |  |

| 2     | addi x2,x1,0×1              | lw x1 | ,0×10(x0)  |                                         |                    |          |  |

| 3     | add x3,x2,x1                | addi  | There isn' | t enough space t                        | o show this – afte | er cvcle |  |

|       |                             | 1 7   |            | 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 5 |                    |          |  |

11, this add instruction will exit the pipeline.

addi x2,x1,0×1

add x3, x2, x1

addi

4

5

6

8

9

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

sw  $x3,0 \times 14(x0)$

add x0, x0, x0

addi xz, xı, v×ı

add x3, x2, x1

add x3, x2, x1

add x3, x2, x1

sw  $x3,0 \times 14(x0)$

# <u>WITHOUT</u> EX->EX & Mem->EX Forwarding

What's the CPI of the pipeline for the first three instructions?

Cycles = 11, Instructions =

$$3$$

=> CPI =  $11/3 \sim = 3.67$

$$CPI = \frac{Cycles}{Instructions}$$

What's the IPC of the pipeline for the first three instructions?

$$IPC = \frac{Instructions}{Cycles}$$

Ideally, you'd want IPC to get as close to 1 as possible.

# WITH EX->EX & Mem->EX Forwarding

|       |                |    |    | 3   |    |

|-------|----------------|----|----|-----|----|

| Cycle | IF             | ID | EX | Mem | WB |

| 1     | lw x1,0×10(x0) |    |    |     |    |

|       |                |    |    |     |    |

|       |                |    |    |     |    |

addi  $x2, x1, 0 \times 1$  | lw  $x1, 0 \times 10(x0)$

$lw x1,0 \times 10(x0)$

# WITH EX->EX & Mem->EX

| 5-  | -Stage Pipeli | ned Executi | on | Forwarding |    |

|-----|---------------|-------------|----|------------|----|

| cle | IF            | ID          | EX | Mem        | WB |

lw x1,0×10(x0)

addi  $x2, x1, 0 \times 1$

$lw x1,0 \times 10(x0)$

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

# WITH EX->EX & Mem->EX

| 5-Stage Pipelined Execution |    |    |    | Forwarding |    |

|-----------------------------|----|----|----|------------|----|

| Cycle                       | IF | ID | EX | Mem        | WB |

$lw x1,0 \times 10(x0)$

# <u>WITH</u> EX->EX & Mem->EX Forwarding

$lw x1,0 \times 10(x0)$

| Cycle | IF             | ID             | EX             | Mem | WB |

|-------|----------------|----------------|----------------|-----|----|

| 1     | lw x1,0×10(x0) |                |                |     |    |

| 2     | addi x2,x1,0×1 | lw x1,0×10(x0) |                |     |    |

| 3     | add x3,x2,x1   | addi x2,x1,0×1 | lw x1,0×10(x0) |     |    |

addi **x2**,**1**,0×1

addi references a value in x1, but the previous

lw has not yet put a new value in x1 yet!

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

# WITH EX->EX & Mem->EX Forwarding

$lw x1,0 \times 10(x0)$

Solution: (same as last time) insert a pipeline bubble in the EX

stage to force the addi to wait until x1 has the new value.

|       | Olago i ipoli  |                | Forwarding     |     |    |

|-------|----------------|----------------|----------------|-----|----|

| Cycle | IF             | ID             | EX             | Mem | WB |

| 1     | lw x1,0×10(x0) |                |                |     |    |

| 2     | addi x2,x1,0×1 | lw x1,0×10(x0) |                |     |    |

| 3     | add x3,x2,x1   | addi x2,x1,0×1 | lw x1,0×10(x0) |     |    |

|       |                |                | ~~~            |     |    |

# <u>WITH</u> EX->EX & Mem->EX Forwarding

| Cycle | IF             | ID                            | EX                           | Mem            | WB                     |

|-------|----------------|-------------------------------|------------------------------|----------------|------------------------|

| 1     | lw x1,0×10(x0) |                               |                              |                |                        |

| 2     | addi x2,x1,0×1 | lw x1,0×10(x0)                |                              | Mom >EV        | forwardings            |

| 3     | add x3,x2,x1   | addi x2,x1,0×1                | lw x1,0×10(x0)               | Welli->LX      | <del>forwarding!</del> |

| 4     | add x3,x2,x1   | addi x2, <mark>x1</mark> ,0×1 |                              | lw x1,0×10(x0) |                        |

| 5     | sw x3,0×14(x0) | add x3,x2,x1                  | addi x2, <mark>x1,</mark> ∜1 | 1              | lw x1,0×10(x0)         |

|       |                |                               |                              |                |                        |

At the trigger clock edge between cycle 4 and 5, the result of lw becomes available. The pipeline identifies that the following instruction – addi – depends on the result of lw via register x1, and forwards this value to addi as it enters the EX stage.

<u>WITH</u> EX->EX & Mem->EX Forwarding

| Cycle                                                                                                                                                                                                                                                           | IF             | ID                            | EX                            | Mem            | WB             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|-------------------------------|----------------|----------------|

| At the trigger clock edge between cycle 5 and 6, the result of addi becomes available.  The pipeline identifies that the following instruction – add – depends on the result of addi via register x2, and forwards this value to add as it enters the EX stage. |                |                               |                               |                |                |

| 4                                                                                                                                                                                                                                                               | add x3,x2,x1   | addi x2, <mark>x1</mark> ,0×1 |                               | lw x1,0×10(x0) |                |

| 5                                                                                                                                                                                                                                                               | sw x3,0×14(x0) | add x3,x2,x1                  | addi x2, <mark>x1</mark> ,0×1 | 1              | lw x1,0×10(x0) |

| 6                                                                                                                                                                                                                                                               | add x0,x0,x0   | sw x3,0×14(x0)                | add x3, <mark>x2</mark> ,x1   | addi x2,x1,0×1 |                |

|                                                                                                                                                                                                                                                                 |                |                               |                               | EX->EX forv    | varding!       |

|                                                                                                                                                                                                                                                                 |                |                               |                               |                | <b>.</b>       |

|                                                                                                                                                                                                                                                                 |                |                               |                               |                |                |

#### WITH EX->EX & Mem->EX **Forwarding**

| Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IF                                                                   | ID                                                        | EX                                               | Mem                                                                                                                              | WB              |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| The point of the p | pipeline identifies<br>egister x3, and fo<br>that this forwardi      | that the following rwards this value ing still happens to | g instruction – sweeto sweeto sweeto as it enter | sult of add become — depends on the stage.  The stage in the true in the stage in the stage in the stage in the control signals. | e result of add |  |

| 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | add x0,x0,x0                                                         | sw x3,0×14(x0)                                            | add x3,x2,x1                                     | addi x2,x1,0×1                                                                                                                   | 1               |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | add x0,x0,x0 add x0,x0,x0 sw x3,0×14(x0) add x3,x2,x1 addi x2,x1,0×1 |                                                           |                                                  |                                                                                                                                  |                 |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |                                                           |                                                  | EX->EX forv                                                                                                                      | varding!        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |                                                           |                                                  |                                                                                                                                  |                 |  |

$lw x1,0 \times 10(x0)$

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

add x0, x0, x0

add x0, x0, x0

add x0, x0, x0

sw  $x3,0 \times 14(x0)$

2

3

4

5

6

7

8

| <u>WI7</u> | <u> H</u> E | X->EX | & | Mem->EX |

|------------|-------------|-------|---|---------|

| For        | war         | ding  |   |         |

$lw \times 1,0 \times 10(x0)$

addi  $x^2, x^1, 0 \times 1$

sw  $x3,0 \times 14(x0)$

add x3, x2, x1

**WB**

$lw \times 1,0 \times 10(\times 0)$

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

Mem

$lw x1,0 \times 10(x0)$

addi  $x2, x1, 0 \times 1$

sw  $x3,0 \times 14(x0)$

add x3, x2, x1

add x0, x0, x0

| 5- | Stage | Pipeli | ned | Executi | on |

|----|-------|--------|-----|---------|----|

|    |       |        |     |         |    |

Cycle IF

ID EX

$lw x1,0 \times 10(x0)$

addi  $x2,x1,0\times1$

addi  $x2, x1, 0 \times 1$

sw  $x3,0 \times 14(x0)$

add x3, x2, x1

add x0, x0, x0

add x0, x0, x0

# 5 Stage Dipoliped Execution

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x3, x2, x1

add x0, x0, x0

add x0, x0, x0

add x0, x0, x0

add x0, x0, x0

sw  $x3.0 \times 14(x0)$

3

4

5

6

7

8

9

| WITH EX->EX | <b>8</b> | Mem->EX |

|-------------|----------|---------|

| Forwarding  |          |         |

|             |          |         |

$\times 10(x0)$

addi  $x2, x1, 0 \times 1$

add x3, x2, x1

add x0, x0, x0

With forwarding, the third instruction

exits the pipeline after the 8th cycle.

addi  $x^2, x^1, v^1$

sw  $x3,0 \times 14(x0)$

add x3, x2, x1

add x0,x0,x0

| 5-Stage Pipelined Execution |    |    | OH | Forwarding |    |  |

|-----------------------------|----|----|----|------------|----|--|

| Cycle                       | IF | ID | EX | Mem        | WB |  |

|                             |    |    |    |            |    |  |

add.

add x3, x2, x1

add x0, x0, x0

add x0, x0, x0

sw  $x3,0 \times 14(x0)$

$lw x1,0 \times 10(x0)$

$lw x1,0 \times 10(x0)$

addi  $x2, x1, 0 \times 1$

addi  $x2, x1, 0 \times 1$

sw  $x3,0 \times 14(x0)$

add x3, x2, x1

add x0, x0, x0

add x0, x0, x0

add x0, x0, x0

<u>WITH</u> EX->EX & Mem->EX

Forwarding

What's the CPI of the pipeline for the first three instructions?

Cycles = 8, Instructions =

$$3$$

=> CPI =  $8/3 \sim 2.667$

$$CPI = \frac{Cycles}{Instructions}$$

What's the IPC of the pipeline for the first three instructions?

$$IPC = \frac{Instructions}{Cycles}$$

IPC is no way near 1 yet, but it's better than 0.273.

### Iron Law of Computer Performance

CPU Time =

$$\frac{\text{Instructions}}{\text{Program}} \times \frac{\text{Cycles}}{\text{Instruction}} \times \frac{\text{Seconds}}{\text{Cycle}}$$

From without forwarding to with forwarding, we've improved CPI:

CPI Improvement =

$$\frac{8/3}{11/3} = \frac{8}{11}$$

### Speedup again?

From without forwarding to with forwarding, we've improved CPI:

CPI Improvement =

$$\frac{8/3}{11/3} = \frac{8}{11}$$

That is, the new CPU Time is 8/11 of the original CPU Time. How much speedup did we just get?

$$S = \frac{t_{\text{base}}}{t_{\text{improved}}} = \frac{t_{\text{base}}}{\frac{8}{11} \times t_{\text{base}}} = \frac{11}{8} = 1.375$$

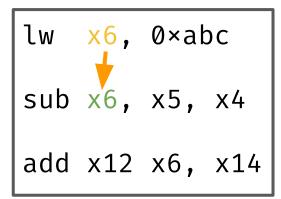

### Pipeline hazards

We've already seen this:

Cycla

ID

| Cycle | 1              | טו<br>         |                               | IVICITI        | VVD |

|-------|----------------|----------------|-------------------------------|----------------|-----|

| 1     | lw x1,0×10(x0) |                |                               |                |     |

| 2     | addi x2,x1,0×1 | lw x1,0×10(x0) |                               |                |     |

| 3     | add x3,x2,x1   | addi x2,x1,0×1 | lw x1,0×10(x0)                |                |     |

| 4     |                |                | addi x2, <mark>x1</mark> ,0×1 | lw x1,0×10(x0) |     |

Mam

W/R

ΕY

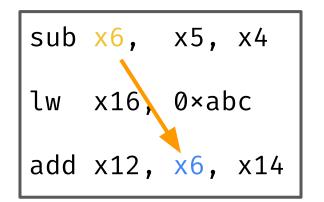

This is the Read-After-Write (RAW) hazard, the only possible hazard type in our

addi <u>reads</u> an incorrect value from x1 in EX, <u>then</u>, lw <u>writes</u> to x1.

This is the Read-After-Write (RAW) hazard, the only possible hazard type in our simple 5-stage pipeline.

Read-After-Write (RAW)

Can happen in our pipeline.

Write-After-Read (WAR)

Can happen in an (incorrectly implemented) out-of-order pipeline.

Write-After-Write (WAR)

Can happen in an (incorrectly implemented) out-of-order pipeline.

# Labs

#### Lab<sub>0</sub>

Recitation 0 and 1 should have everything you need for finishing Lab 0.

https://course.ece.cmu.edu/~ece344/course\_documents/18344-f25-recitation0.pdf

https://course.ece.cmu.edu/~ece344/course\_documents/18344-f25-recitation1.pdf

#### Lab 1

- Starting from Lab 1, labs will be partnered (in most cases, group of 2)

- We **recommend** using proper version control tools

- e.g. git; MAKE SURE YOUR REPO IS PRIVATE IF

#### **USING GITHUB OR ALTERNATIVES**

- Not likely that we can be of much help if you nuked your work on the number machines

- Schedule regular meetings with your lab partner

- This is more important than you'd think

- Watch out for an announcement on the "code freeze" policy

- Expect a code deadline a few days before the report deadline