# F01 Project 2: Transistor-Level Equiv. Checking

- **▼** So far, the "logic" we have seen is all made of *gates*

- ▶ AND, OR, EXOR, EXNOR, NOT etc etc

- But, ICs are made up from transistors

- ▶ CMOS P- and N-type FETs to be precise

- How can we look at a transistor-level netlist and "extract" the Boolean logic function it implements, and then "check" this?

- ▶ This is project 2

- ▶ Need a good transistor-level representation as Boolean values

- ▶ Need to simplify away some transistor-level behavior

- ▶ Need to know new techniques for solving systems of Boolean eqns

- ► All doable with BDDs (of course!)

© R. Rutenbar 2001, CMU 18-760, Fall 2001 1

## **Copyright Notice**

© Rob A. Rutenbar 2001 All rights reserved.

You may not make copies of this material in any form without my express permission.

## Where Are We?

■ A *very* realistic application...

|                 | M                         | Т                               | W                               | Th                        | F                        |                                 |

|-----------------|---------------------------|---------------------------------|---------------------------------|---------------------------|--------------------------|---------------------------------|

| Aug             | 27                        | 28                              | 29                              | 30                        | 31                       | 1                               |

| Sep             | 3                         | 4                               | 5                               | 6                         | 7                        | 2                               |

|                 | 10                        |                                 | 12                              | 13                        | 14                       | 3                               |

| Oct             | 17                        | 18                              | 19                              | 20                        | 21                       | 4                               |

|                 | 24                        | 25                              | 26                              | 27                        | 28                       | 5                               |

|                 |                           | 2                               | 3                               | 4                         | 5                        | 6                               |

|                 | 8                         | 9                               | 10                              | П                         | 12                       | 7                               |

|                 | 15                        | 16                              | 17                              | 18                        | 19                       | 8                               |

|                 |                           |                                 |                                 |                           |                          | _                               |

|                 | 22                        | 23                              |                                 | 25                        | 26                       | 9                               |

|                 | 22<br>29                  |                                 |                                 |                           |                          | _                               |

| Nov             |                           | 23                              | 24                              |                           | 26                       | 9                               |

|                 | 29                        | 23<br>30                        | 24<br>31                        | 25<br>1                   | 26                       | 9                               |

|                 | <b>29 5</b>               | 23<br>30<br>6                   | 24<br>31<br>7                   | 25<br>1<br>8              | 26 2 9                   | 9<br>10<br>11                   |

| Nov             | 29<br>5<br>12             | 23<br>30<br>6<br>13             | 24<br>31<br>7<br>14             | 25<br>7<br>8<br>15        | 26<br>2<br>9<br>16       | 9<br>10<br>11<br>12             |

| Nov             | 29<br>5<br>12<br>19       | 23<br>30<br>6<br>13<br>20       | 24<br>31<br>7<br>14<br>21       | 25<br>1<br>8<br>15<br>22  | 26<br>2<br>9<br>16<br>23 | 9<br>10<br>11<br>12<br>13       |

| Nov<br>Thnxgive | 29<br>5<br>12<br>19<br>26 | 23<br>30<br>6<br>13<br>20<br>27 | 24<br>31<br>7<br>14<br>21<br>28 | 25<br>8<br>15<br>22<br>29 | 26<br>2<br>9<br>16<br>23 | 9<br>10<br>11<br>12<br>13<br>14 |

- **▼ OUT:** 16 Oct 2001

- **■** DUE: 8 Nov 2001 by 5pm

#### **▼** Logistics:

- ▶ You can work in groups of 2

- ► Implementation is in C or C++ using the CUDD BDD package from U Colorado. You link to it.

#### **▼** For a grade

- ► Writeup is a WEBPAGE. You put it up, email us the URL by 5pm

- ▶ DEMO required, sign-up for times at end of project, will be required to show performance on "live" (new) circuits, explain what happens as they run in real-time.

© R. Rutenbar 2001, CMU 18-760, Fall 2001 3

# Readings/Deadlines/Projects

#### ■ De Micheli

▶ Nothing about this stuff

#### **▼** Deadlines

- ▶ OK, fine, I give up: HW3 due date BACK to Oct 23, NEXT Tue, in class

- > AFTER mid-semester break

#### ▼ Project #2

- ▶ Today—the overview

- ▶ Due date: 8 November 2001

# **Background: CMOS Logic**

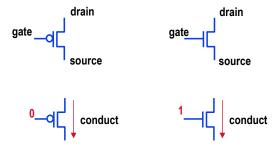

#### ■ 2 kinds of transistors: P and N

- ▶ N devices conduct when their input == I

- ▶ P devices conduct when their input == 0

- ▶ Devices have 3 terminals, are bidirectional for us

© R. Rutenbar 2001, CMU 18-760, Fall 2001 5

# **Our Problem**

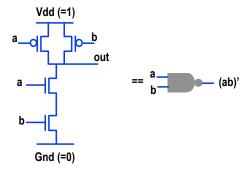

- How do we analyze a transistor netlist and "extract" Boolean functions for its outputs?

- ▶ For example, how can we compute that this netlist is a simple NAND?

- ▶ This is a pretty simple case: this is a static CMOS (series/parallel) gate

# **Our Problem**

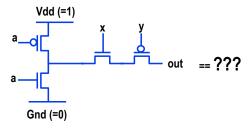

- And what if we allow pass transistor style circuits?

- ▶ The 2 devices at the left are clearly a simple inverter

- ▶ But, the inverted output passes thru 2 pass transistors which can "gate" the result to the output only if x==1, y==0

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 7

## **Our Problem**

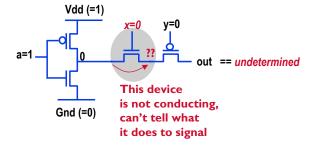

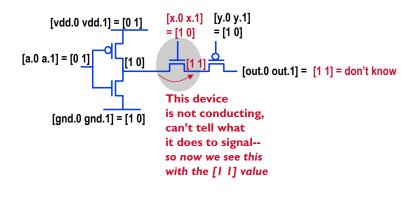

- And what happens when signals take "unreasonable" values?

- ► Can allow inputs to be "unknown" in logic networks, see how these unknowns propagate

- ▶ But, in a transistor netlist, all signals can be known, and the output may still be undetermined; consider example below

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 8

### **Solution**

- Need a more sophisticated model of the "steady state" value on a wire in a transistor netlist

- ▶ "Steady state" means combinational circuits only, when they stabilize

- ▶ Need to model not just "=1" and "=0" but also "=X" don't know state

- Need to acknowledge some simplifications

- ▶ All devices have same "strength", as do all storage nodes in circuit

- ▶ No ratio tricks, no overriding of logic values at contended node, etc.

- ► Some crazy dynamic circuits, circuits with complex state, won't work in our analysis technique

- Need more powerful solution strategy

- ▶ With a good model for individual nodes in the MOS circuit, we can derive systems of Boolean equations. Trick is in how to solve them...

© R. Rutenbar 2001, CMU 18-760, Fall 2001 9

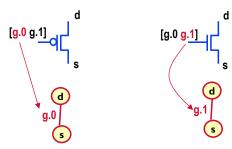

### **Better Model of Logic Nodes**

- **▼** Use 2-bit signal encoding -- just like PCN notation

- ► Each node (wire) in a netlist gets a pair of boolean variables that together represent its state

- ▶ So, node "p" represented as [p.0 p.1] pair of values

- ▶ Same encoding as PCN

```

\triangleright [p.0 p.1] = 0 l => it's a Boolean l

```

- $\triangleright$  [p.0 p.1] = 1 0 => it's a Boolean 0

- ▷ [p.0 p.1] = 1 1 => it's indeterminate -- don't know what it is

- $\triangleright$  [p.0 p.1] = 0 0 => not allowed to happen

#### **▼** Goal

- ▶ We want the "ordinary" Boolean values (0, 1) to work like ordinary logic gates work

- ▶ But we want to get [I I] when a node in the circuit simply cannot be determined from the current inputs. In other words we want to compute and to propagate these indeterminate values correctly

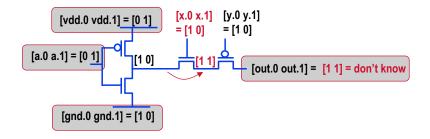

# Simple Example

**▼** This is what we expect we should be able to compute

© R. Rutenbar 2001, CMU 18-760, Fall 2001 11

# **Inputs and Outputs**

- **■** Look again at this example

- ▶ Notice that the inputs and the outputs and even the power rails are also represented in this same notation

▶ Need to be careful to be precise about what is a variable and what is a constant here...

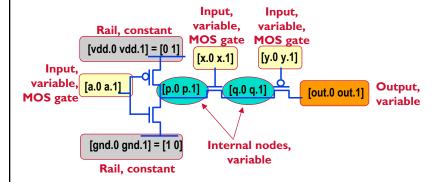

## Nodes in Netlist: Inputs, Outputs, Internal

- 4 kinds of nodes (wires) in these circuits, with diff constraints

- ▶ Inputs:

- > represented as variables, can be connected to MOS gates or to MOS drain/source. You need to know which--it will matter later

- ▶ Power rails:

- be they are inputs, but special inputs with constant value, they are not variables, they appear to us as constant "1" or "0"

- **▶** Outputs:

- > represented as variables, can connect only to MOS drain/src

- ▶ Internal:

- > everything else in the circuit. Represented as variables. These represent MOS device drains and sources

© R. Rutenbar 2001, CMU 18-760, Fall 2001 13

## Nodes in Netlist: Inputs, Outputs, Internal

### **▼** Example revisited

What we want is to create a BDD for every internal and output node [v.0 v.1] that captures the correct behavior, ie, [v.0=(some BDD), v.1=(some other BDD)]

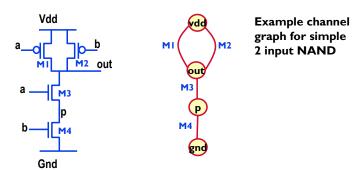

# Solving for Node Equations

- **▼** 5 big steps

- **1.** Make the diffusion channel graph for the circuit

- ▶ Graph represents paths thru the circuit we need to model

- **■** 2. Solve for v.1 var for each [v.0 v.1] internal & output node

- ▶ Graph lets us create a set of simultaneous Boolean eqns; solve 'em

- 3. Solve for v.0 var for each [v.0 v.1] internal & output node

- ▶ Similar graph, different variables, same solution process

- 4. Solve for D=indeterminate conditions for each int/out node

- ▶ Similar graph, different vars, same solution process

- **5.** Assemble final solution

- ▶ From v.I, v.0, D at each variable node, we can get Bool eqn we need

© R. Rutenbar 2001, CMU 18-760, Fall 2001 15

### **Channel Graph**

- **▼** Represents conducting paths in the CMOS circuit

- ▶ Node = MOS transistor drains and sources. NOT the MOS gate inputs.

- ▶ Edge = one MOS device drain-source path, ie, conducting channel

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 16

# **Channel Graph**

### **▼** Our other example

Example channel graph for Inverter with "odd" pass devices at its output

© R. Rutenbar 2001, CMU 18-760, Fall 2001 17

## **Using the Channel Graph**

### **▼** Channel graph defines a *system* of Boolean equations

- ► We need to know how to set these up, this is how we will solve for v.I, v.0 and D for each node in the circuit

- ► We specify a set of "initial" values for the graph, where a "value" is a Boolean equation.

- ▶ Each node and each edge gets an initial value

- ▶ Each node then gets a variable, call it x[n] for node n

- ▶ Goal is to solve for x[n] at each node so that the overall set of Boolean equations defined by the graph is "consistent", ie, makes sense, works out right under some sensible rules

### **₹**3 big questions

- ▶ What does such a system of Boolean equations look like?

- ▶ What does a "consistent" Boolean solution look like?

- ▶ Mechanically, how do we solve to find this solution?

## **Analogy: Systems of Linear Equations**

- Analogy: matrices from linear algebra

- ▶ We have variables, say: t y z w

- ▶ We have a system of linear equations, for example

$$2t + 3y + 4z + 5w = 32$$

$t + 7z - 3w = 10$

$7t + 3y + w = 17$

$2y + 3z + 8w = 45$

► A consistent solution -- in this case, t=1 y=2 z=3 w=4 -- is such that if you take any row of this matrix and substitute these values in, the equation checks out right, eg

$$2t + 3y + 4z + 5w = 32$$

$t + 7z - 3w = 10$

$7t + 3y + w = 17$  =>  $7(1) + 3(2) + (4) = 17$  ...yes, OK

$2y + 3z + 8w = 45$

► A linear solver (eg, Gaussian elimination) can take this system, and having only the 4x4 matrix (call it A) and the 4x1 vector (call it b), can solve the eqn Ax = b for the solution x vector=[1 2 3 4]

© R. Rutenbar 2001, CMU 18-760, Fall 2001 19

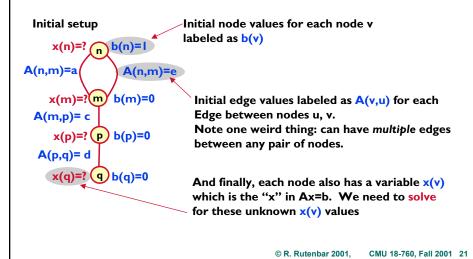

### **Now: Systems of Boolean Equations**

- Amazingly enough, the *same* problem

- ▶ Only now, we have "AND" for "•" and "OR" for "+"

**Initial setup**

Initial node values are like the "b" constants in a linear algebra Ax=b matrix problem.

But, for us, they are boolean eqns

Initial edge values are like the elements of the "A" matrix in a linear algebra Ax=b problem. But, for us, they are again boolean eqns

# Now: Systems of Boolean Equations

■ Relabel the graph to make this association clear

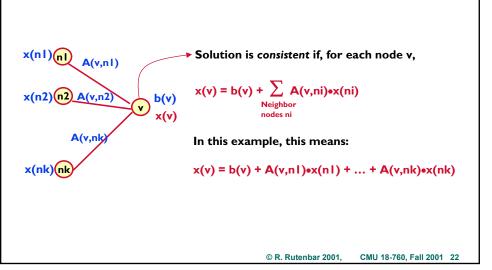

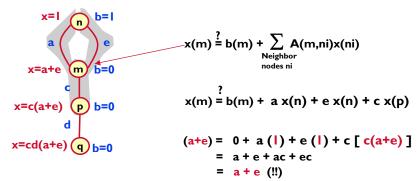

## **Solving Systems of Boolean Equations**

- Now do we recognize a solution? It's "consistent", it "works"

- ▶ Here is the rule for when a set of eqns for each x(v) "works":

### **Example**

#### **▼** A consistent solution

### **New questions**

- ▶ Properties of this solution?

- ▶ And, how do we actually find such a solution?

© R. Rutenbar 2001, CMU 18-760, Fall 2001 23

### **Solution Properties**

### **▼** The big, useful result (Bryant 1989)

- ▶ Any Boolean system [A b] where A is a set of edge values (boolean eqns) and b is a set of node values (boolean eqns) has a UNIQUE solution x (set of node eqns)

- ▶ This solution is given by the limit of the sequence x<sup>i</sup>, where

- $\triangleright x^0(v) = b(v)$  for all nodes v

$$> x^{i}(v) = x^{i-1}(v) + \sum_{\substack{\text{Neighbor} \\ \text{nodes } n}} A(v,n)x^{i-1}(n)$$

#### **▼** In English...

- ▶ There's one unique solution to the set of equations

- ▶ You can find it iteratively--

- > Set all x(v) to b(v) to start

- ▶ Pick a node, update it with the above formula based on its neighbors

- Continue until each x(v) equation stops changing

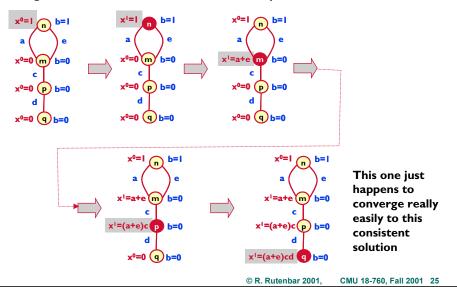

## **Solving Iteratively**

- **▼** Showing the iterations:

- ▶ go thru each node, do this formula on it, update x<sup>0</sup> value to x<sup>1</sup> value

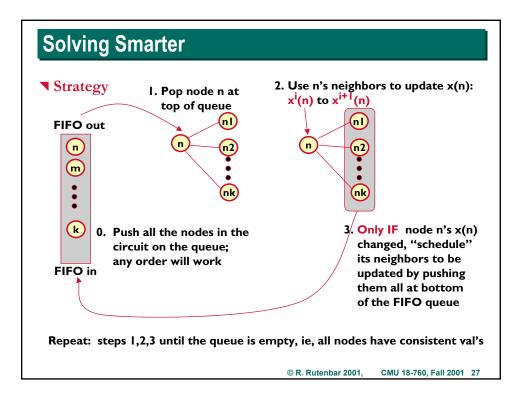

### **Solving Smarter**

- Not smart to update the nodes in totally "random" order

- Randy Bryant in CS (who invented this) says:

- "...if you keep doing updates of the form v[i] <-- v[i] OR a[i,j] AND v[j] you'll eventually get a convergent solution. Since you're using BDDs, the convergence test becomes feasible. Basically, it then works a lot like the fixed point iterations of model checking.

I think you'll find the iterative method works just fine. The main thing is to set up an "event list" that propagates an update only if the value on the source changes. This should be processed in FIFO order, so that you get the equivalent of breadth first expansion."

### **Aside: Solving VERY Smart**

- Iterative is OK, not the best you can do

- ▶ Just like with linear systems

- ▶ Smartest you can do with (nice) linear systems: Gaussian elimination

- ▶ Smartest you can with these Boolean systems: Gaussian elimination

- **▼** Yes--you <u>can</u> do Gaussian elimination on these systems

- ▶ Check class web site, I'll post the papers from Bryant

- ▶ More complicated, but optimally fast for larger designs

- ▶ You don't have to do it for this project (but you can if you want to...)

### **OK: Where Are We?**

#### ■ We have a workable model for the circuit

- ▶ Each node (internal, rail, input, output) is a 2-bit [v.0 v.1] pair

- ► Model supports the indeterminate "X" I-don't-know-value state, and propagates it correctly

- ▶ Channel graph models the circuit correctly for us

### **▼** We know how to solve systems of Boolean equations

- ▶ Iteratively till convergence

- ▶ Just like Ax=b, but A=edges, b=nodes, x(v) = unknowns on each node, and each of these is a Boolean equation

#### **▼** What's left?

▶ What system(s) of equations do we need to set up whose solution is the right answer for the behavior of these circuits?

© R. Rutenbar 2001, CMU 18-760, Fall 2001 29

## **Setting Up the Equations**

#### **■ 3** sets of equations to solve

- ▶ First 2 will seem "natural" when you see them

- ▶ Last one is not so intuitive (at first)

#### **▼** Strategy

- ▶ Set up and solve the equations to determine v.l at each node

- ▶ Set up and solve the equations to determine v.0 at each node

- ▶ Look closely and these and see why they are not sufficient

# Solving for v.1 & v.0

#### **▼** Rules

- ▶ Build channel graph for the circuit

- ▶ Defn: the definite value for a MOS gate input [g.0 gl] is:

- N FET: this is g.I (ie, if g.I=on, then this N FET conducts)

- ▷ P FET: this is g.0 (ditto--if g.0 in on, P FET conducts)

- ▷ (Ignore the [I I] "X" state for now; we'll come back to this)

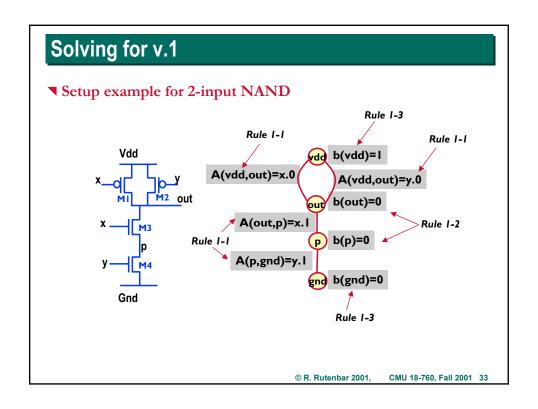

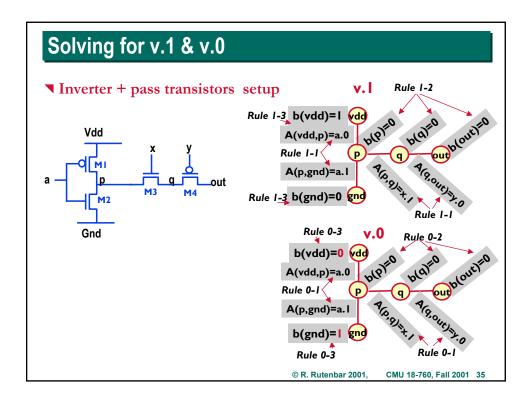

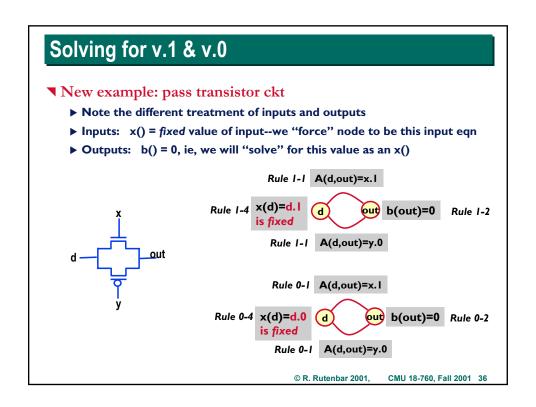

# Solving for v.1 & v.0

#### **▼** To setup to solve v.1:

▶ Rule I-I: edge value A(u,v) is the definite value for the FET associated with this edge in the diffusion graph

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 31

- ▶ Rule I-2: b(v) value for an internal node is 0. A node is internal if not connected to an input var, or a power rail

- ▶ Rule I-3: b(v) value for a rail is <u>I</u> if the rail is Vdd, <u>0</u> if rail is Gnd

- ▶ Rule I-4: x(v) value for a drain/source -connected input is i.! where "i" is the name of the input variable. Do NOT resolve for this x(v), it's fixed.

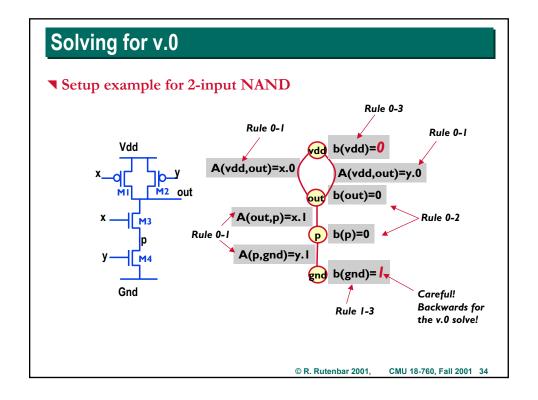

#### **▼** To setup to solve v.0 (almost identical):

- ▶ Rule 0-1: edge value A(u,v) is the definite value for the FET associated with this edge in the diffusion graph

- ▶ Rule 0-2: b(v) value for an internal node is 0. A node is internal if not connected to an input var, or a power rail

- ▶ Rule 0-3: b(v) value for a rail is 0 if the rail is Vdd, I if rail is Gnd

- ► Rule 0-4: x(v) value for a drain/source -connected input is i.0 where "i" is the name of the input variable. Do NOT resolve for this x(v), it's fixed.

# Doing the Solve (In Detail...)

#### ▼ Mechanically

```

//Each non-fixed node v gets an unknown Boolean equation x(v)

for(each node v in graph){

if (node v is a diffusion input )

set x(v) to fixed BDD eqn for input node // we won't try to solve for this one

else {

set x(v) == b(v) BDD;

push node v onto FIFO queue;

while (FIFO not empty) {

v = pop top node on FIFO

create x^{new}(v) = x(v)

for(each node n that is a neighbor of node v)

x^{\text{new}}(v) = x^{\text{new}}(v) + A(v,n)*x(n)

// Compare x^{new}(v) and x(v) -- they're BDDs, it's easy to compare!

if (x^{new}(v) == x(v))

//Great -- don't reschedule all its neighbor nodes n for update

let x(v) = x^{new}(v)

// x^{new}(v) != x(v), so, schedule all neighbor nodes n for update

for( each neighbor node n of v)

if( node v is not a fixed diffusion input)

push n onto the FIFO queue;

Replace x^{new}(v) with x(v)

}

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 37

```

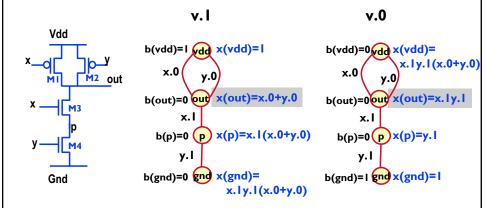

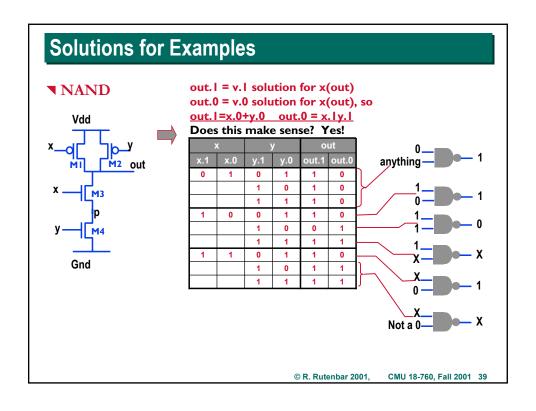

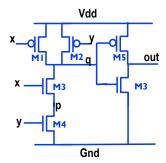

## **Solutions for Examples**

#### **▼** NAND

The boolean equations for the output nodes are what we care about

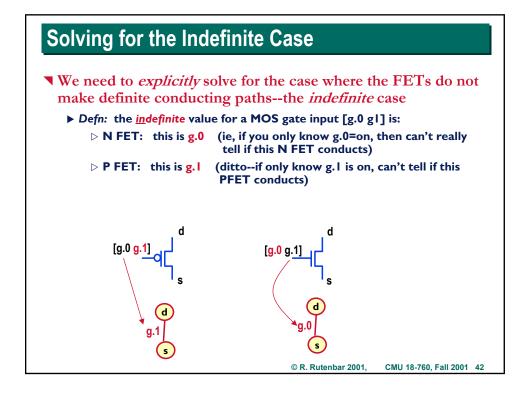

## **Solving for the Indefinite Case**

- Same solution strategy, but different system setup rules

- ▶ Rule d-1: edge value A(u,v) is the complement of the indefinite value for the FET associated with this edge in the diffusion graph

- ► Rule d-2: b(v) value for an internal node is 0. A node is internal if not connected to an input var, or a power rail

- ▶ Rule d-3: b(v) value for any rail is I

- ▶ Rule d-4: x(v) value for any drain/source -connected input is fixed at 1

- **▼** Rules are similar, interpretation is more subtle

- ▶ Set up and solve this system for x(v)

- ▶ Take the resulting x(v) and complement each one, !x(v)

- ► Update v.l solution: out.l = out.l + !x(out)

- ► Update v.0 solution: out.0 = out.0 + !x(out)

- **▼** Look at examples again...

© R. Rutenbar 2001, CMU 18-760, Fall 2001 43

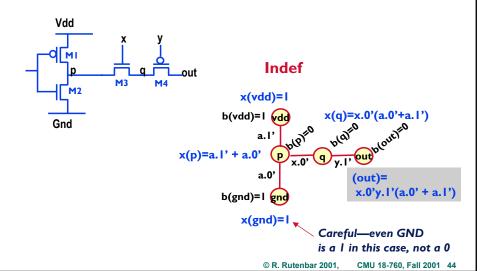

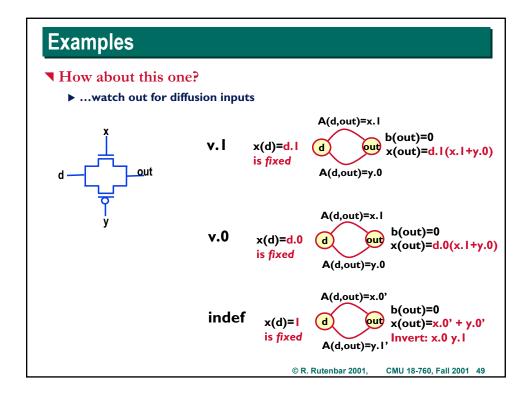

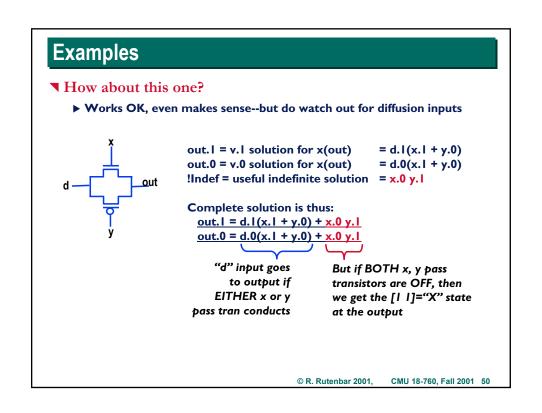

## **Examples: Indefinite Solution**

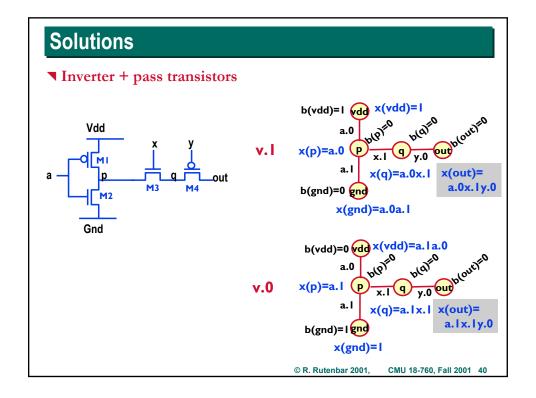

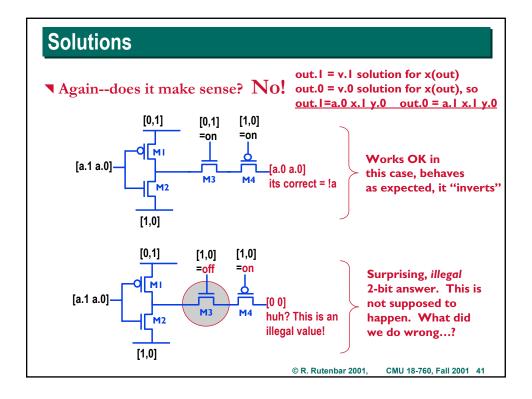

**▼** Inverter + pass transistors

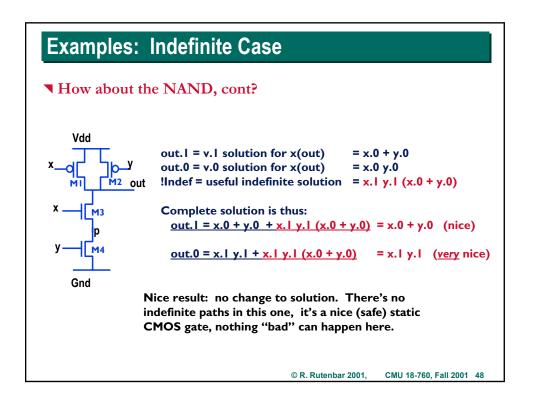

## **Examples: Indefinite Case**

#### **■** Mechanics of final solution

```

\begin{array}{lll} \text{out.1} = \text{v.1 solution for } x(\text{out}) & = \text{a.0 x.1 y.0} \\ \text{out.0} = \text{v.0 solution for } x(\text{out}) & = \text{a.1 x.1 y.0} \\ \text{Indef} = \text{"raw" indefinite solution} & = \text{x.0' y.1' } (\text{a.0' + a.1'}) \text{ ; we must invert} \\ \text{!Indef} = \text{useful indefinite solution} & = \text{x.0 + y.1 + a.1a.0} \\ \end{array}

```

Complete solution is thus:

out.

$$I = a.0 \times l y.0 + x.0 + y.l + a.la.0$$

out.0 = a.l x.l y.0 +

$$x.0 + y.l + a.la.0$$

#### **▼** How this works

- ▶ (!Indef) captures the cases where the paths are not defined in the MOS network, because FETs are not "for sure" conducting, OR their own gate inputs are in the "X" state

- ▶ When (!Indef)==I, it means "can't tell if there's a path to a I,0 here"

- ▶ By ORing (!Indef) into both out. I and out.0, we force the out value to be [I I] in these cases, which is the "X" encoding, which is answer we want

© R. Rutenbar 2001, CMU 18-760, Fall 2001 45

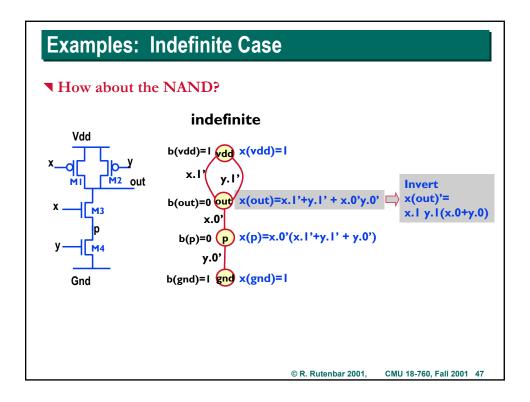

### **Examples: Indefinite Case**

**▼** OK, now does it make sense? Yes!

Complete solution is :

out.1 = a.0 x.1 y.0 + x.0 + y.1 + a.1a.0out.0 = a.1 x.1 y.0 + x.0 + y.1 + a.1a.0

|       |     |     | ,   |     |     |     |       |       |

|-------|-----|-----|-----|-----|-----|-----|-------|-------|

|       | x.1 | x.0 | y.1 | y.0 | a.1 | a.0 | out.1 | out.0 |

| ıs, ʃ | -   | 1   | -   | -   | -   | -   | 1     | 1     |

| ) [   | -   | -   | 1   | -   | -   | -   | 1     | 1     |

| ("-{  | -   | -   | -   | -   | 1   | 1   | 1     | 1     |

| or√   | 1   | 0   | 0   | 1   | 0   | 1   | 1     | 0     |

| ר זע  |     |     |     |     | 1   | 0   | 0     | 1     |

Indefinite cases for pass trans, or impossible input case [0 0]

If input = "X", then output ="X".

Expected out = !a behavior

# So, Where Are We?

- **▼** To analyze a transistor level netlist

- ▶ Read in netlist

- ▶ Build channel graph for it

- ▶ Set and solve, in order: v.l system, v.0 system, indef system

- ▶ Construct solution BDD for each output node

- Dut.I = v.I solution + !(indef solution)

- Dut.0 = v.0 solution + !(indef solution)

- ▶ Result is a pair of BDDs [Out.0 Out.1] that correctly describe behavior of the output node, including "X" behavior and "indefinite path" behav

- **▼** What's missing here...?

- ▶ One little thing...

© R. Rutenbar 2001, CMU 18-760, Fall 2001 51

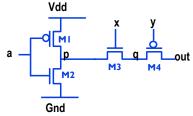

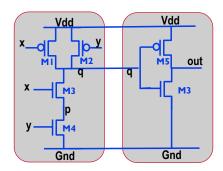

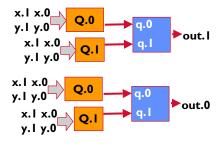

# Multiple, Disconnected Channel Graphs

- **▼** Real netlists have many distinct channel-connected regions

- ▶ You have to analyze each one separately using these solver techniques

- ▶ Then, you need to "glue" the final solution together, in the right order

2 channel graphs in here

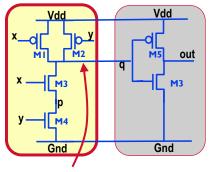

# **Multiple, Disconnected Channel Graphs**

### **▼** Simple strategy

▶ You have to analyze each one separately using these solver techniques

Analyze the NAND first. Build [Q.0 Q.1] solution for its output node.

1. Compute Q=[Q.1 Q.0]

© R. Rutenbar 2001, CMU 18-760, Fall 2001 53

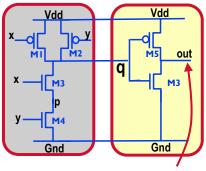

# Multiple, Disconnected Channel Graphs

### **▼** Simple strategy

▶ You have to analyze each one separately using these solver techniques

Treat input q as just another atomic variable.

Build BDDs for [out.1 out.0]

2. Analyze INVERTER second.

2. Compute out=[out.1 out.0]

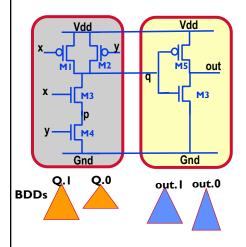

# Multiple, Disconnected Channel Graphs

### **▼** Simple strategy

▶ Then, you need to "glue" the final solution together, in the right order

Replace input var "q" in the INVERTER result with BDDs for Q using composition

© R. Rutenbar 2001, CMU 18-760, Fall 2001 55

### **Mechanics**

#### **▼** You need to read in the netlist

▶ There's a simple format for transistor netlists

### **▼**You DO NOT need to identify each individual channel graph

- ▶ We will provide you with labeling to ID the channel connected parts

- ▶ But, you need to build a new graph which lets you determine the right order in which to glue together the results for individual channel graphs

### ■ You need to analyze the function of each channel graph

- ▶ Determine the inputs/outputs. Inputs may be "temp" variables.

- ▶ Set up and solve the v.l v.0 & indef systems for each graph

### **▼** Glue the final answers together

▶ Requires you to visit the channel graphs in the right order, and to substitute variables in the right order

# Format: Basic Transistor Netlist

```

NUMMODS <number_of_transistors>

NUMNETS <number_of_nets>

NUMINPUTPADS <number_of_inputs>

NUMOUTPUTPADS <number_of_outputs>

VDD <VDD_net_num>

GND <GND_net_num>

INPUT <input_1_net_num>

INPUT <input_2_net_num>

..... for all circuit inputs

OUTPUT <output_1_net_num>

... for all circuit outputs

P1 <channel graph ID> <source> <qate> <drain>

P2 <channel graph ID> <source> <gate> <drain>

N1 <channel graph ID> <source> <gate> <drain>

.... for all transistors

END

Some comments on the net numbers

-> If we convert from a gate-level netlist,

(1) .. (VDD-1) are gate-level node numbers

(GND+1) .. (NUMNETS) are the new nodes introduced

© R. Rutenbar 2001,

CMU 18-760, Fall 2001 57

```

# **Example:** Basic Transistor Netlist

```

--- Example File c17.TRAN -----

NUMMODS 24

NUMNETS 19

NUMINPUTPADS 5

NUMOUTPUTPADS 2

VDD 12

GND 13

INPUT 1

INPUT 2

INPUT 3

INPUT 4

TNPIIT 5

OUTPUT 6

OUTPUT 7

P1 1 12 1 8

N1 1 8 1 14

P2 1 12 3 8

N2 1 14 3 13

P3 2 12 3 9

N3 2 9 3 15

P4 2 12 4 9

N4 2 15 4 13

P5 3 12 2 10

N5 3 10 2 16

P6 3 12 9 10

N6 3 16 9 13

```

```

P7 4 12 9 11

N7 4 11 9 17

P8 4 12 5 11

N8 4 17 5 13

P9 5 12 8 6

N9 5 6 8 18

P10 5 12 10 6

N10 5 18 10 13

P11 6 12 10 7

N11 6 7 10 19

P12 6 12 11 7

N12 6 19 11 13

END

```

### **Format: Basic Gate-Level Netlist**

### **■** Why do we need this?

▶ So you can compare not just transistor netlists, but a transistor netlist against the gate-level logic netlist its supposed to be implementing...

```

NUMMODS <number_of_gates>

NUMMETS <number_of_nets>

NUMNETS <number_of_inputs>

NUMOUTPUTPADS <number_of_outputs>

INPUT <input_1_net_num>

INPUT <input_2_net_num>

..... for all circuit inputs

OUTPUT <output_1_net_num>

... for all circuit outputs

GATE_TYPE <num_inputs> <input1> <input2> ... <output_node>

... for all gates

END

```

© R. Rutenbar 2001, CMU 18-760, Fall 2001 59

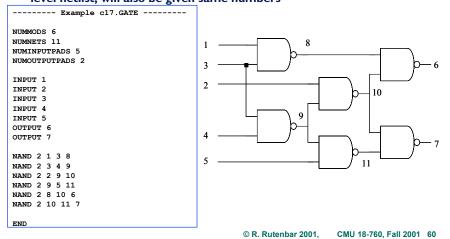

### **Example: Basic Gate-Level Netlist**

- This is the same circuit (c17) but at gate level

- ▶ We guarantee that the input and output var numbers are same

- ▶ Also, any "nodes" in the gate level netlist that still exist in the transistor level netlist, will also be given same numbers

Page 30

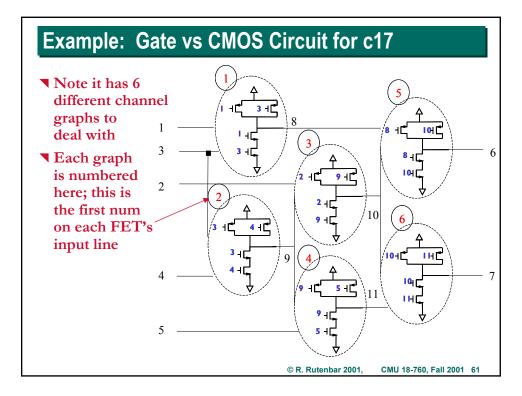

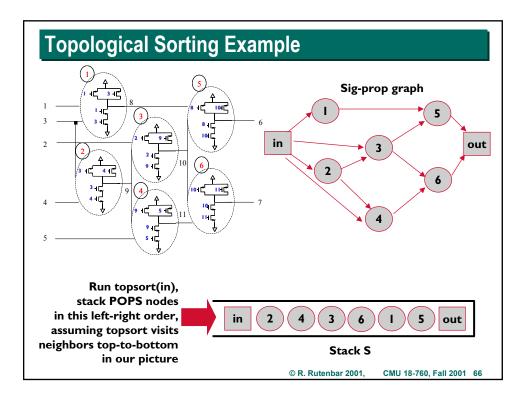

### **How to Deal with Different Channel Graphs**

- **▼** We will ID which graph each transistor belongs to, in input file

- ► You need to make a 2nd graph, to tell you in which order to glue together the results of the boolean analysis of each channel graph

- ▶ Call this graph the "signal propagation" graph

- Building the sig-prop graph

- ▶ One distinguished vertix called "input"

- ▶ One distinguished vertex called "output"

- ▶ One vertex for each channel graph (labled in input deck)

- ▶ Directed edge <u>from</u> "input" node <u>to</u> any channel graph node that connects to an external input

- ▶ Directed edge <u>from</u> any channel graph node <u>to</u> the output node for every channel graph that connects to an external output

- ▶ Direct edge from one channel graph node N to another channel graph node M if a MOS diffusion output from N connects to a MOS gate input in M

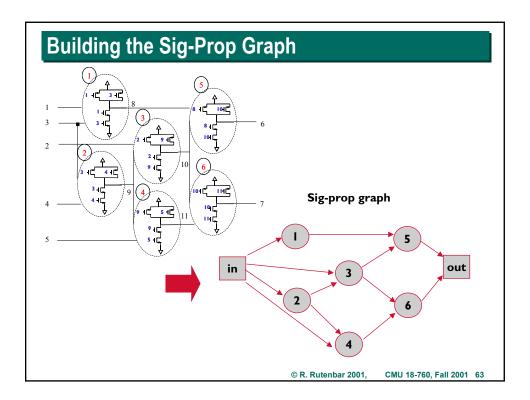

# **Using the Sig-Prop Graph**

- **▼** What do we do with it?

- ▶ We use it to determine the right order in which to connect the Boolean equations we have for node outputs to node inputs between diffusion graphs

- **■** But--wait, isn't the right order for this example 1-2-3-4-5?

- ▶ Yes, but this one just got numbered in the right order

- ▶ In general, you CANNOT count on the channel graph ID being the same as the proper order

- **■** How do we order the nodes in the graph properly?

- ► Topological sorting

- ▶ A nice, simple depth-first search algorithm on the sig-prop graph

# **Topological Sorting**

- Basic algorithm setup

- ► Every node in sig-prop graph has a flag, initialized = "clear" (untouched)

- ▶ We also need a global stack to store the nodes, call it S

- **▼** Recursive algorithm is a variant of depth first search

```

topsort( sig-prop graph node N) {

mark node N as "first time we have seen it"

for( each node v that is adjacent to node N) {

if ( flag(v)==clear )

topsort( v )

mark node N as "touched" (ie, we are done with it)

push node N on global stack S

}

```

- **▼** To sort the sig-prop graph, just run topsort(in-node)

- ▶ Result is nodes in right order, when you POP them off stack S

## **Putting It All Together**

### **▼** Overall algorithm

```

Read input transistor netlist

build sig-prop graph

topsort(in node)

while (global stack S not empty) {

G = POP stack S

if ( G is unique input or output node in sig-prop)

continue

allocate (possible temporary) vars for BDDs for G's inputs

compute x.0, x.1, x.indef for each vertex in channel graph G

compute final x.0 x.1 solution for each output in channel graph G

for (each MOS gate input "a" in graph G connected to the

output of some other MOS device in the netlist) {

substitute the BDD (equation) already computed for "a" from

a previous channel graph into the BDDs for each output of G

}

}

```

► At this point, you have a BDD for out. I out. 0 for every "real" output of this transistor level netlist

© R. Rutenbar 2001, CMU 18-760, Fall 2001 67

### So, What Do You Actually Do?

- Build a program that...

- ▶ Reads in either:

- > (1) 2 transistor netlists or

- > (2) a transistor netlist and a gate netlist

- ▶ Build the BDD behavior representation of each netlist you read in. Easy for the gate netlist. A lot more work for the transistors.

- ▶ Output whether the netlists are the same or not, logically

- ▶ If not, output something "illuminating", like some counter example input values

- One final technical trick...

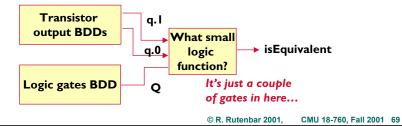

- ▶ How do we compare transistor and gate-level netlists?

# **Comparing Logic to CMOS**

- Our transistor analysis supports "X", but we don't expect you to do this for the gate-level netlists

- ▶ So, each CMOS node will have [q.0 q.1] BDDs built for it

- ▶ But, the SAME node in the gate-level description just gets BDD Q

- ▶ How to compare

- Simple answer: ignore the "X" stuff

- ▶ Only insist that the "real" Is and 0s outputs always agree

- ▶ Ignore the other possibilities, ie, [q.0 q.1] = [0 0] or [1 1]

## **For Credit**

#### **▼** Logistics

▶ You can work in groups of 2 or alone. STRONGLY suggest 2 people

#### **▼** Code

- ► C++ on SUN Solaris or on IBM AIX

- ➤ You get to use a "real" BDD package, CUDD from U Colorado Boulder.

- ▶ See class web page for more info/examples on how to use CUDD

#### ■ Checking

- ▶ We will provide a CHECKER program that can tell you if your code is doing the *right* thing.

- ➤ You will have to dump program output in a specified form for the CHECKER to check.

- ▶ We will make an executable of CHECKER publicly available

### For Credit

### **▼** Writeup

- ▶ Not paper. Web page. You submit it to us via email of the URL.

- ▶ PLEASE make it portable: we copy the whole directory structure to our machines to grade it. If you put absolute pathnames, links, it messes up

- **▶** Suggestion

- ▶ Make a directory: <yourname>760Web, eg, bubba760Web

- ▷ Inside it, put all your html web pages: foo\*.html

- ▷ Inside it, also make 2 directories: 760Stuff and 760Code

- ▷ Inside 760Stuff, put ALL your graphics and pics and sounds and explanatory video clips, etc. Inside 760Code, put all your code.

- ▷ If its on the machine in your dorm room, and it will disappear at random times--TELL US WHEN.

- ▷ If we don't see a web page, you don't get a grade...

- ▶ As in all things in 760 (and in life): style counts

© R. Rutenbar 2001, CMU 18-760, Fall 2001 71

### **For Credit**

- **■** About Writeup--basic pieces

- ▶ Introduction: summarize the problem

- ▶ Formulation: you had to make some assumptions, since there are some degrees of freedom in this project. Explain them. Justify them.

- ▶ Optimization goals: tell us what you tried to do well.

- ▶ Implementation: describe any interesting data structures, algorithms, optimizations, tricks, etc

- ▶ Results: what did you run, how well did you do?

- > Explain your results: why did they happen like this

- ▶ Post mortem: given you could do it over, what would you do different?

- ▶ Code: put it someplace in the web page (preferably in 760Code dir)

## **For Credit**

#### **▼** You have to *demo*, too

- ▶ Last week of project on a couple days--signup sheets

- ▶ We will release some new benchmarks during the demo, and ask you to run 3 of them. They will be small; available in a couple of flavors.

- ▶ You should print something enlightening

- ▶ You run the CHECKER, we look over your shoulder and see what it says

- ▶ Goal: it works, it gives an OK answer.

© R. Rutenbar 2001, CMU 18-760, Fall 2001 73

## Points = [120] (But Weighted Big Overall)

#### **▼** Breakdown

- ▶ [30 pts] Web Writeup: Approach & Implementation

- ▶ [30 pts] Web Writeup: Results & Analysis

- ▶ [10 pts] Code: Reasonableness

- ▶ [30 pts] Demo: Works, Quality, Style, Discussion

- ► [20 pts] Coolness

- ▷ Results (you created some bigger benchmarks, you ran them better, your code was faster, your webpage was slicker, etc)

- > You actually implemented Bryant's Gaussian Elimination algorithm, rather than the simpler iterative technique from class

- > Interesting algorithms (more sophisticated attacks)

- ▷ Interesting implementation (eg, did it in PERL, but its not slow...)

- > You have graphical output of the solver process

- **⊳** Etc etc

## **Benchmarks**

■ Will be in /afs/ece/class/ee760/proj2/benchmarks

#### **▼** 5 kinds of test cases

► Level 0: sanity checks with only one diffusion graph in them.

Simple things like one inverter, 2-input

NAND, etc., labeled clearly, for your debugging

► Level 1: sanity checks with <u>multiple</u> diffusion graphs in them.

Simple things like N inverters in a chain, small trees of NAND gates, etc., labeled clearly, for your debugging

▶ Level 2: small transistor-level netlists. You tell us: what are they?

as logical functions.

▶ Level 3: pairs of transistor-level netlists. You tell us: equivalent or

not? If not, give us one counter-example of input values

► Level 4: pairs of netlists, one transistor, one gate-level. You tell us: equivalent or not? If not, give counter-example input values

#### **▼** Size

▶ Num of transistors or gates: from 2 up to a few thousand.