Accomplished

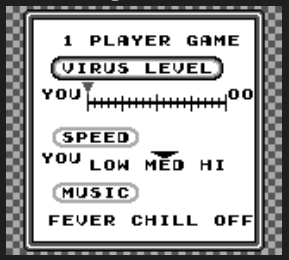

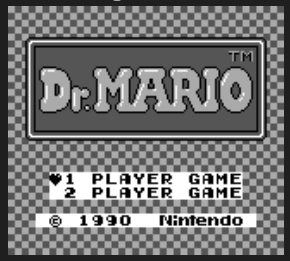

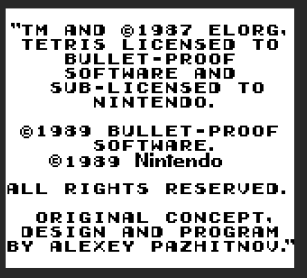

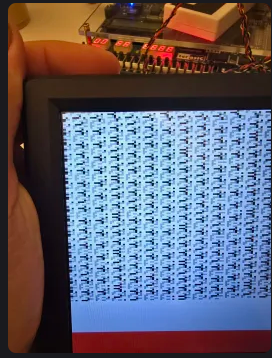

- Debugged Tetris and Dr.Mario on VGA with team. Tetris looks mostly functional but the game appears to run 2x faster. Dr.Mario is stuck after the pill is spawned & before it is thrown.

- I spend some time debugging the issue on simulation. Sadly, this was a fairly slow process as many of the bugs in the games we want to play show up somewhat later so I need to run the simulation for a while to get more information but this still offers a lot more visibility so I am optimistic that I will be able to debug the issue with Dr Mario and Tetris.

- Katherine and I also plan to test a few other games on synthesis.

Next Step(s)

- Finish debugging Dr.Mario and Tetris.

- Prep for demo.

- Work on poster, final report.