Progress:

- CPU:

- Instructions implemented: 103 (all of them)

- Interrupts implemented (needs thorough testing)

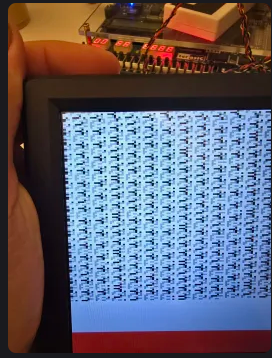

- PPU

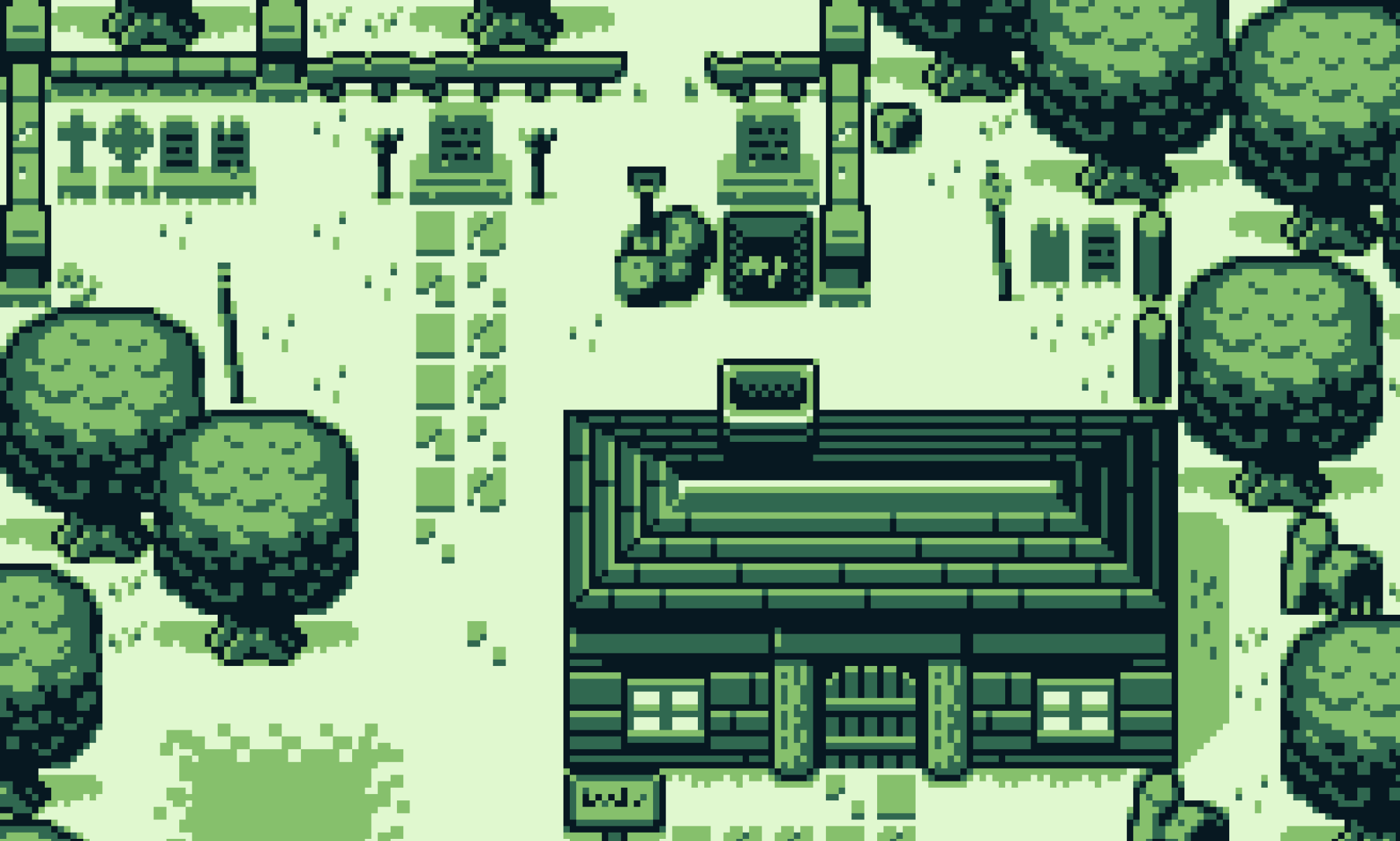

- DMG PPU (4-color PPU) is pretty much done!

- Integrated testing and debugging with VGA logic

- Full-color (CGB) implementation done, debugging in progress

- MMU

- MMU has been written, undergoing debugging and soon-to-be integrated

- APU

- APU writing has started and will be completed soon. Debugging postponed until after MMU/PPU/CPU integration.

- Research into how to use WM8731 (Audio CODEC on the DE2-115)

- Implemented simple I2C based sound check test for the WM8731

- Other I/O

- Spent a lot of time researching USB integration

- Confirmed GPIO NES controller works.

- Resolved NIOS II blocker of lacking library support (had to source specific directory and add to LD_LIBRARY_PATH)

Design Changes:

- Block RAMS are all 16 bit-width, 2 column format (given that the original gameboy’s data is 8 bit data words).

- The reason for this is because we can instantiate dual port RAMS with 16 bit width that can allow OAM entries (32 bit wide) to be accessed in a single clock cycle by the PPU

- Leaving other Block RAMS as 16 bit width as well is reasonable for the CPU and makes things consistent

Risks and Risk Management:

- Switching to Joypad GPIO for now to reduce USB integration complexity

- Postponing NIOS II integration for after MVP gets hit, especially because its more well understood now

Additional Information:

A was written by Bharathi, B was written by Katherine and C was written by Ruslana

Part A — Global factors:

Emulators such as our project help preserve classic video games by allowing people to play them on modern devices, even after the original hardware becomes obsolete. This has global importance, as it makes retro games accessible to people everywhere, regardless of location or resources. Additionally, studying older gaming systems through emulation helps developers understand how past technologies shaped current gaming, inspiring innovation for the future. Our project not only keeps the GameBoy experience alive but also contributes to preserving gaming history on a global scale.

Part B — Cultural factors:

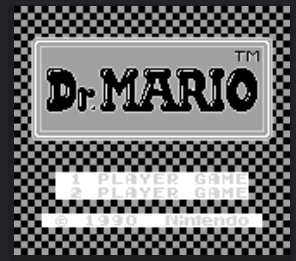

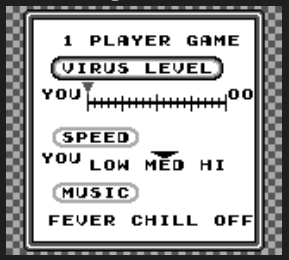

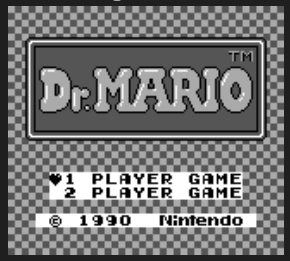

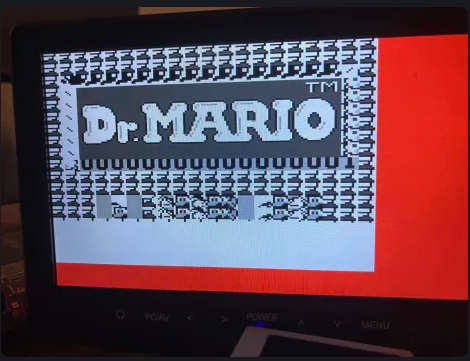

The Gameboy, The console that popularized handheld gaming devices, was discontinued in 2003. It was a significant milestone in gaming history, being the start of many beloved franchises such as Pokemon. However, as time passes, these games, especially lesser-known titles such as Dr. Mario, are fading into obscurity. Our Gameboy emulator helps preserve this gaming history and provides a pathway for the gaming community to reconnect with its roots.

Part C — Environmental factors:

There are several environmental considerations on how our choice to emulate a Gameboy using an FPGA. The greatest benefit of our choice to use an FPGA is the inherent reconfigurable capabilities of an FPGA compared to an ASIC. FPGA development boards can be reprogrammed to serve completely different purposes, and do not require manufacture of new chips. In fact, we were able to avoid incurring any actual cost in our project because FPGAs already exist in the inventory. Once we complete our project, the FPGA can simply be returned and reused for a completely different purpose–therefore, we generate no E-waste with our project.

In addition, if our project succeeds and we open source our FPGA capstone project to other people, they also may be encouraged to enhance or build upon our work. This also can reduce material consumption in the greater community.