Accomplished

My goal for this week was to debug the PPU and scope out what updates would be necessary for the full color implementation.

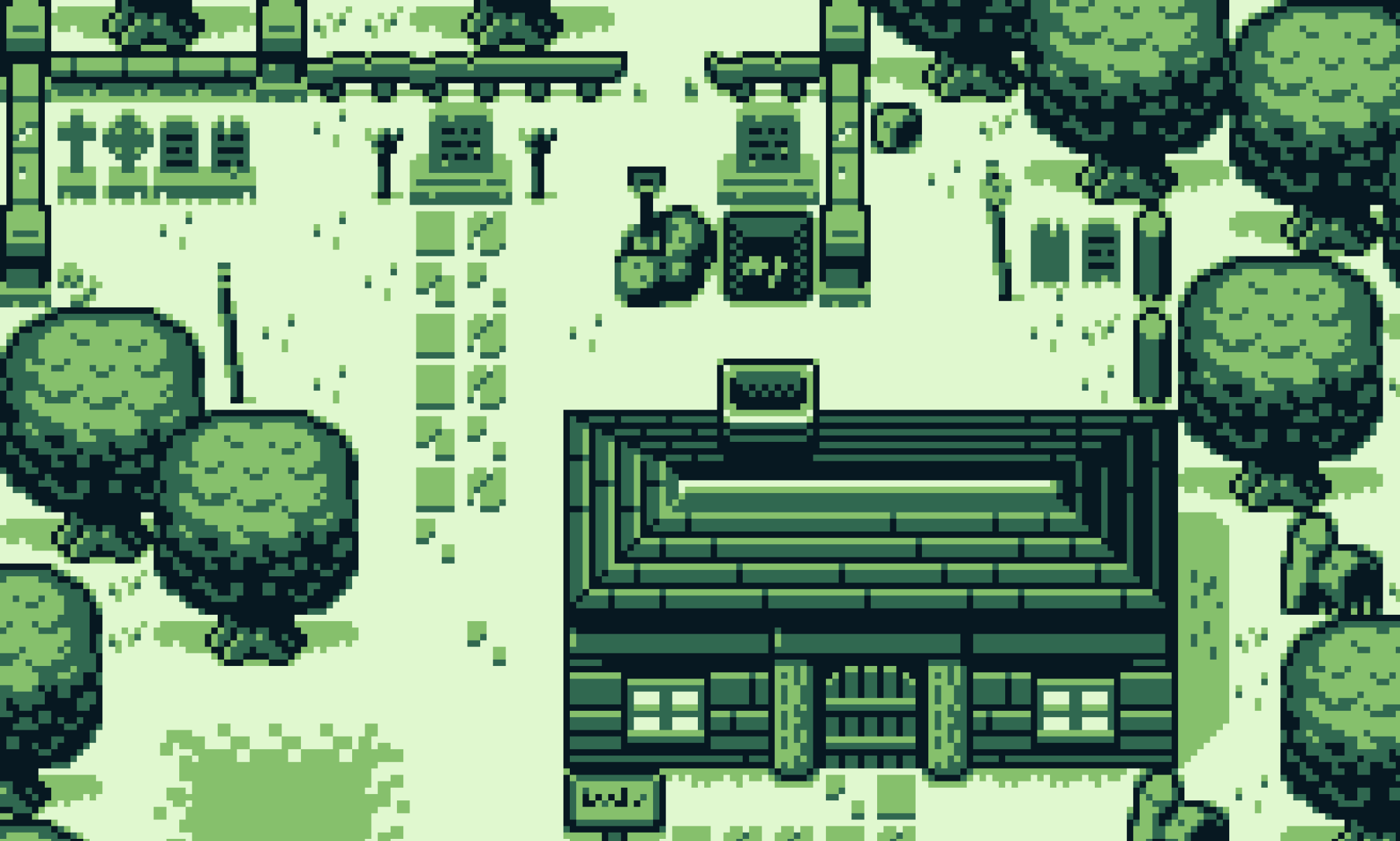

I continued unit testing the PPU and doing complete PPU level single frame and multi-frame tests. I was able to debug a majority of the single frame test cases, but I still have some bugs when rendering frames with more than one sprite. At the moment, I have not integrated the VGA controller logic to test with the FPGA, however, I have been debugging using a custom Python script to render a frame using a pixel array generated using the PPU’s Frame Buffer. Here’s a frame my PPU rendered:

Testing overall has still been a bit of a challenge because in the able of a memory controller and a CPU, my testbench has to be able to simulate the entire environment that the PPU requires. However, I think this is very much worth the effort, as it is likely to make debugging once the full system is integrated much easier. I also spent some time preparing for the Design presentation earlier this week as it was my turn to do the presentation.

Summary of time spent:

- PPU debugging + adding new tests to the testbench : 8 hr

- Full-color design updates research: 3 hr

- Presentation prep + peer review: 3 hr

Schedule / Progress

Overall I think I’m on schedule or slightly behind schedule because I am slightly behind schedule on debugging single frame tests but I started debugging some multi-frame tests and I’ve scoped out what updates/changes will be required for the full-color version. I anticipate that I will be able to get it working full by next weekend.

Next Step

My main goal for next week is to continue debugging the PPU and hopefully also test and profile my implementation a bit after integrating my code with the VGA logic required to test the PPU on the FPGA.