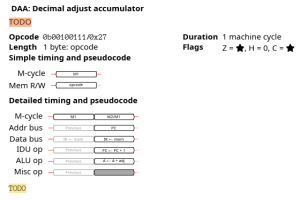

Progress:

- CPU:

- Made testbench to test CPU using Blargg test ROMs

- Almost all CPU Blargg test ROMs pass. (~24M instructions)

- Test 2 (interrupts) requires integration with MMU and PPU to pass.

- PPU

- DMG PPU debug + CGB PPU Updates.

- basic VGA test on FPGA works + VGA & Frame Buffer logic integrated with PPU.

- MMU

- Made personal testbench for MMU

- All basic BRAM tests are passing, currently debugging IO and DMA features. Expected to start integration next weekend.

- APU

- WM8731 I2C reset test works on FPGA –> learned SignalTap on Quartus to get this working.

- Full I2C Config logic implemented + fully works in simulation.

- I2S logic sketched out.

Design Changes:

- Reworked a lot of interrupt routine handling after talk about CPU/MMU

Risks and Risk Management:

- Integration must start by next weekend.